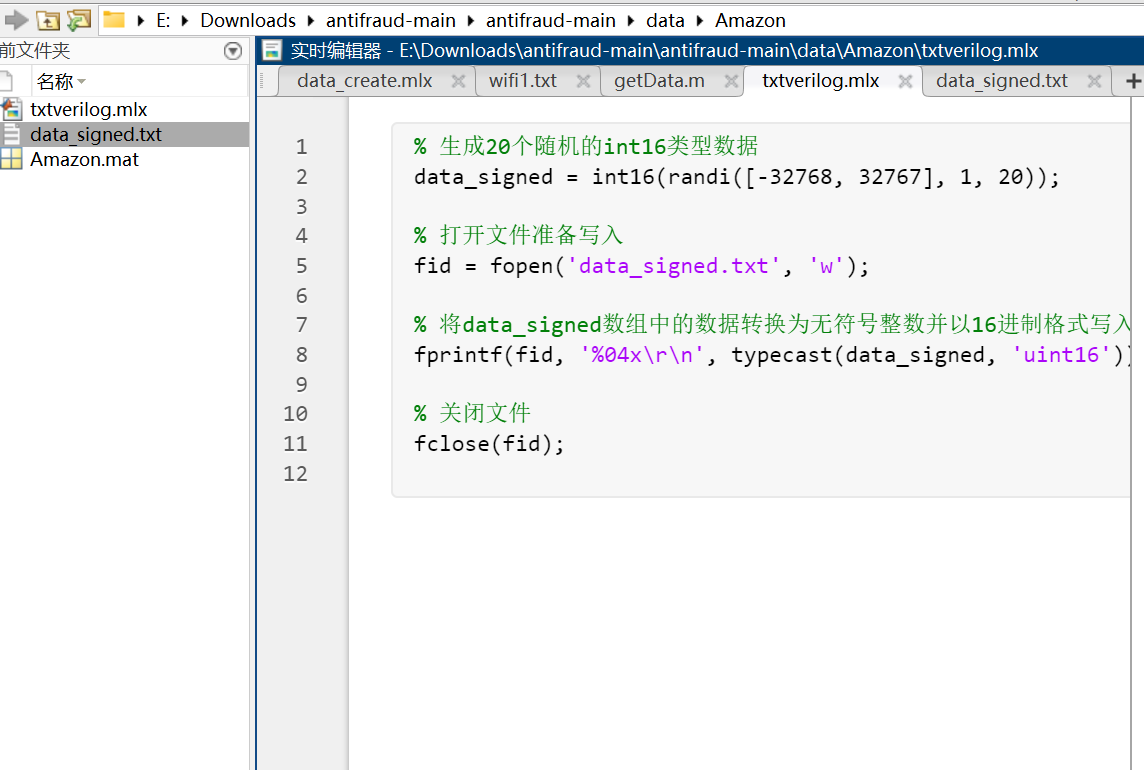

在硬件编程中,接口命名规范也是一个良好的习惯。接口在确定模块划分后需要明确模块的端口以及模块间的数据交互。完成项目模块划分后,可以在确定端口及数据流向时参考使用。本节重点是EN与vld的区别!

`

`

| 信号 | 说明 |

|---|---|

| clk | 模块工作时钟 |

| rst_n | 系统复位信号,低电平有效 |

| en | 门控时钟,请搜索本站关于门控时钟讲解,这是低功耗的设计,EN=0睡眠状态、阻断时钟输入 |

| vld | 数据有效标志指示信号,表示当前的 data 数据有效。注意,vld 不仅表示了数据有效,而且还表示了其有效次数。时钟收到多少个 vld=1,就表示有多少个数据有 |

| data | 数据总线。输入一般名称为 din,输出一般名称为 dout。类似的信号还有 addr,len 等 |

| err | 整个报文错误指示,在 eop=1 且 vld=1 有效时才有效 |

| sop | 报文起始指示信号,用于表示有效报文数据的第一个数据,当 vld=1 时此信号有效 |

| eop | 报文结束指示信号,用于表示有效报文数据的最后一个数据,当 vld=1 时此信号有效 |

| rdy | 模块准备好信号,用于模块之间控制数据发送速度。例如模块 A 发数据给模块 B,则rdy 信号由模块 B 产生,连到模块 A(该信号对于 B 是输出信号,对于 A 是输入信号);B 要确保 rdy 产生正确,当此信号为 1 时,B 一定能接收数据;A 要确保仅在 rdy=1 时才发送 |

![图片[1] - FPGA与数字IC设计中接口命名规范 - 我的学记|刘航宇的博客 图片[1] - FPGA与数字IC设计中接口命名规范 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63e6564a4757feff33d75e79.jpg)