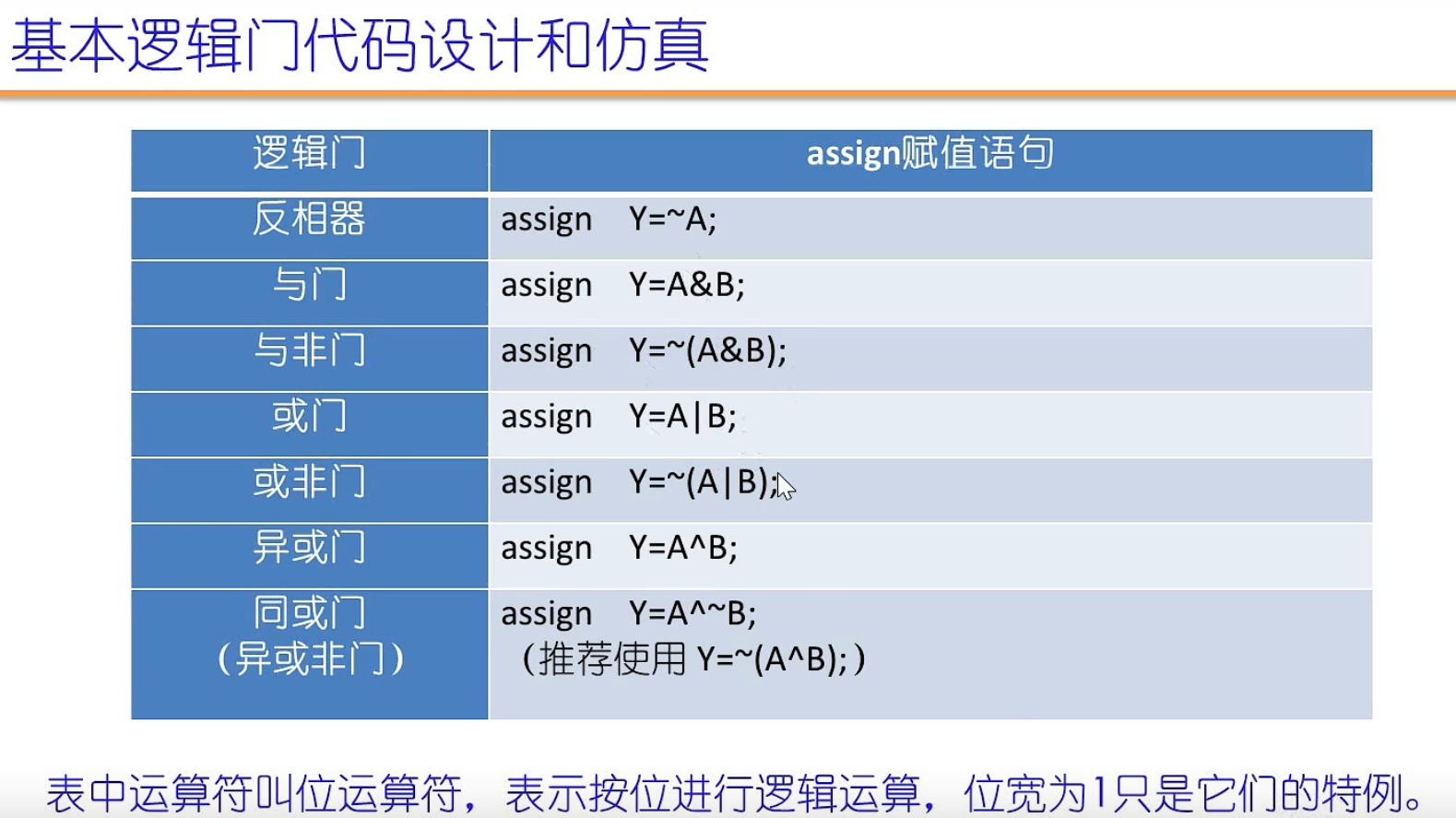

反相器

![图片[1] - 【1】Verilog练习-基本门电路反相器&与非门 - 我的学记|刘航宇的博客 图片[1] - 【1】Verilog练习-基本门电路反相器&与非门 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/6280e9750947543129d08f70.jpg)

//反相器设计

`timescale 1ns/10ps //1ns时间单位,10ps精度

module inv(

A,

Y

);

input A;

output Y;

assign Y=~A;

endmodule

//---testbench of inv--

module inv_tb; //testbench无端口不写括号

reg aa; //输入

wire yy; //输出

inv inv(

.A(aa),

.Y(yy)

); //异名例化

initial begin

aa<=0;

#10 aa<=1; //过10个时间单位timescale

#10 aa<=0;

#10 aa<=1;

#10 $stop;

end

endmodule现象:![图片[2] - 【1】Verilog练习-基本门电路反相器&与非门 - 我的学记|刘航宇的博客 图片[2] - 【1】Verilog练习-基本门电路反相器&与非门 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/6280e8bf0947543129ce3191.jpg)

多位反相器

![图片[3] - 【1】Verilog练习-基本门电路反相器&与非门 - 我的学记|刘航宇的博客 图片[3] - 【1】Verilog练习-基本门电路反相器&与非门 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/6285cbdc09475431295af9b1.jpg)

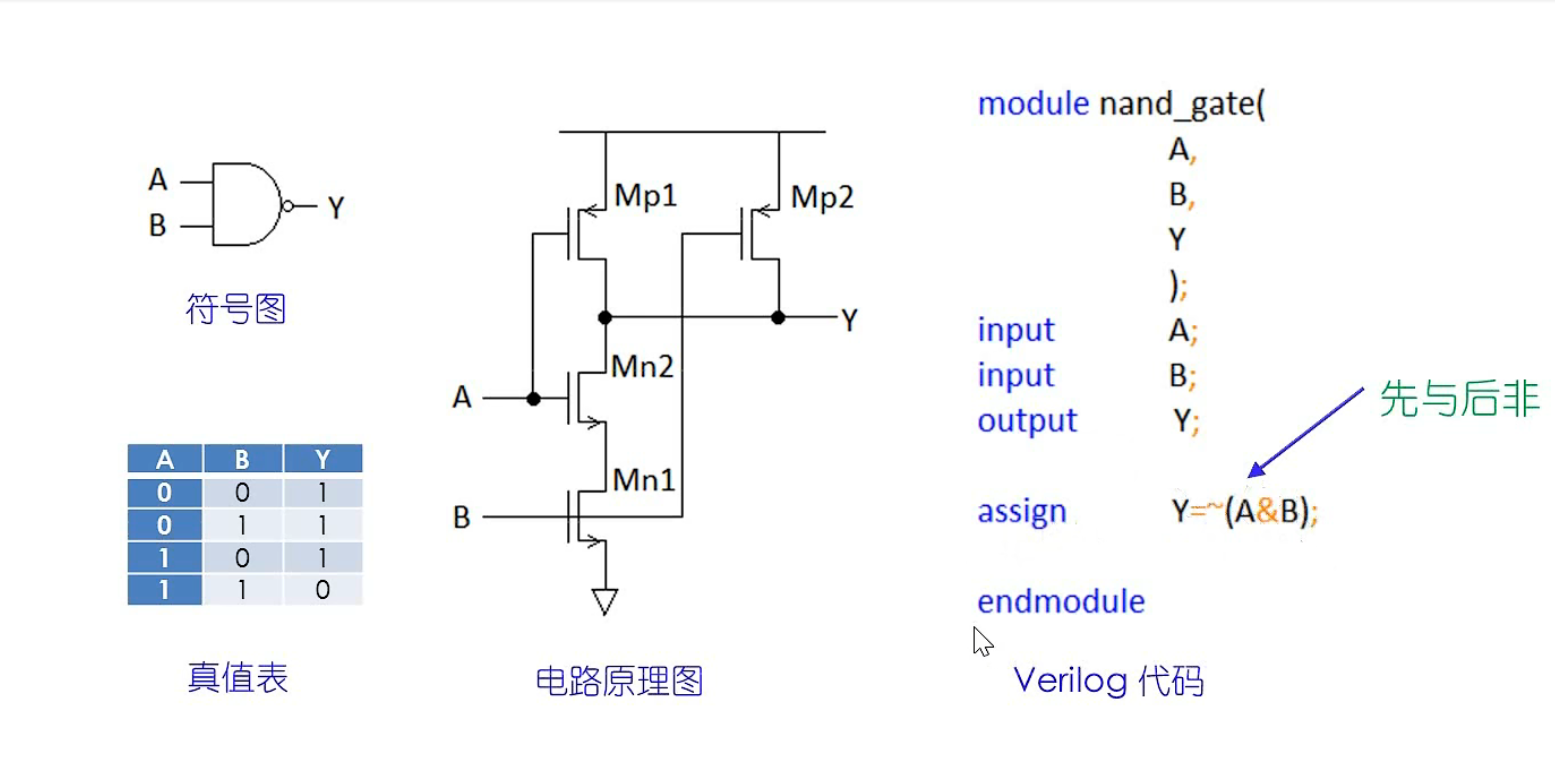

与非门

代码

//与非门

`timescale 1ns/10ps

module nand_gate(

A,

B,

Y

);

input A;

input B;

output Y;

assign Y=~(A&B);

endmodule

//------testbench of nand_gate--

module nand_gate_tb;

reg aa,bb; //输入定义为reg

wire yy;

nand_gate nand_gate(

.A(aa),

.B(bb),

.Y(yy)

);

initial begin

aa<=0;bb<=0; //用箭头等号对应实际电路

#10 aa<=1;bb<=1;

#10 aa<=0;bb<=1;

#10 aa<=1;bb<=0;

#10 aa<=0;bb<=0;

#10 $stop;

end

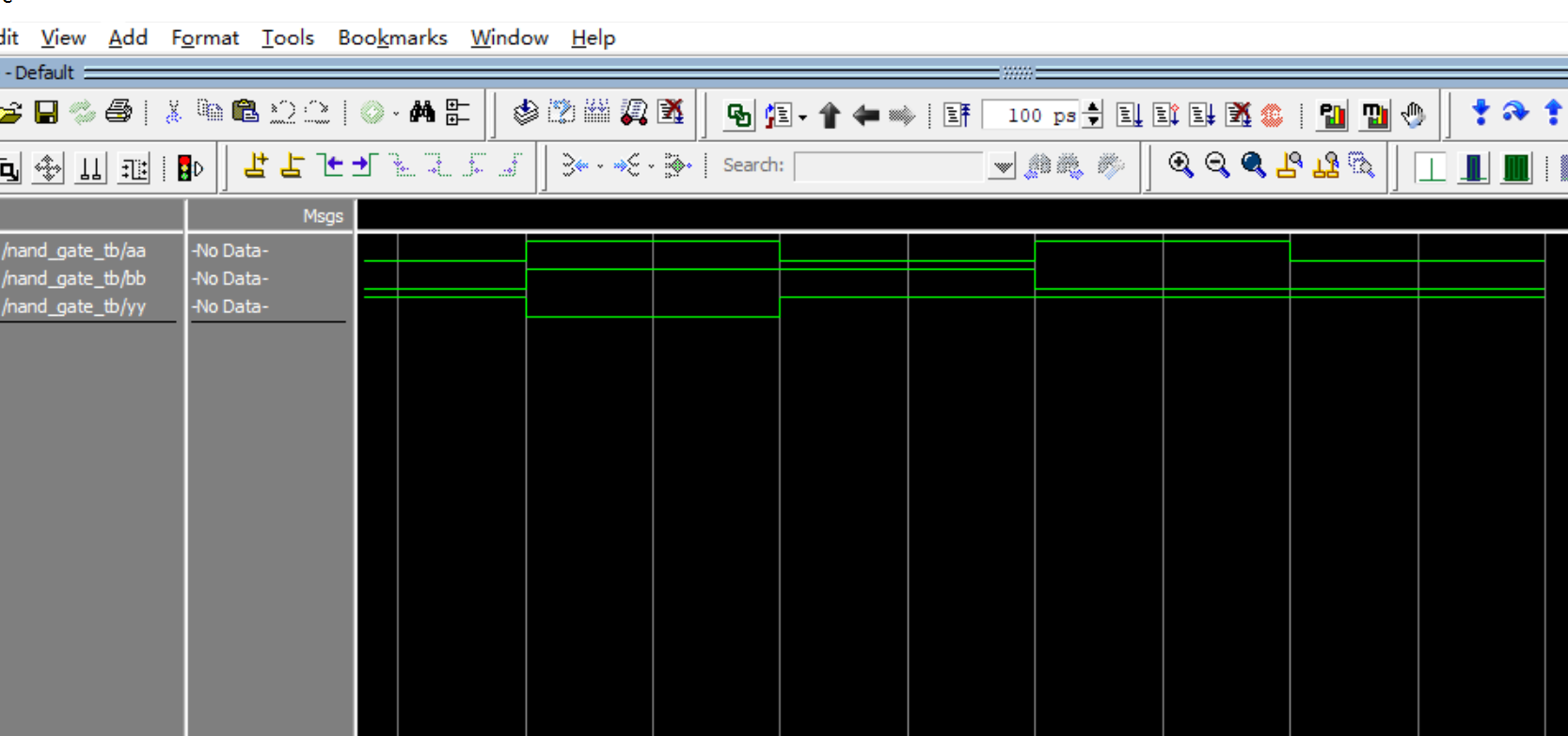

endmodule现象

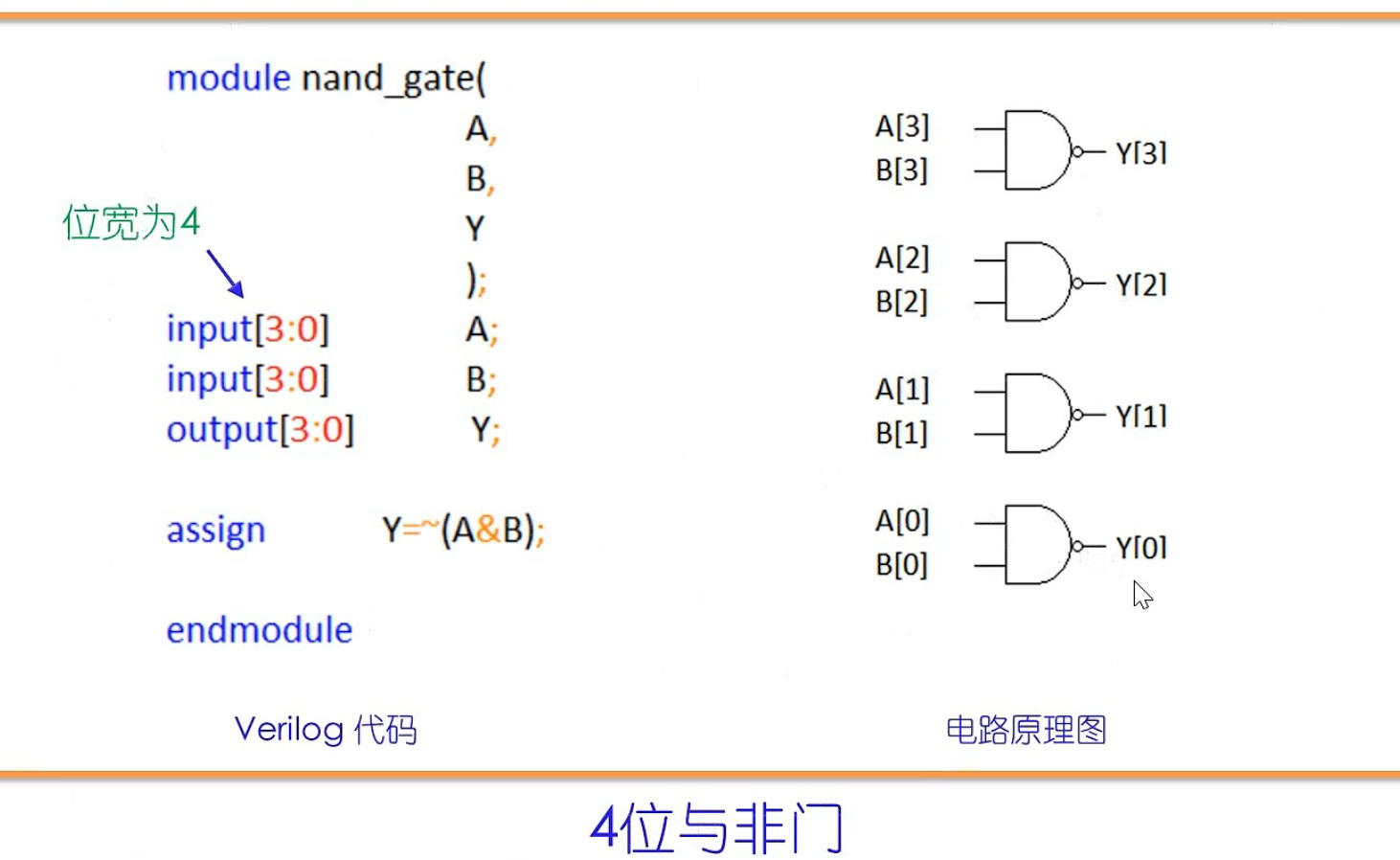

多位与非门

代码

//与非门

`timescale 1ns/10ps

module nand_gate_4bits(

A,

B,

Y

);

input[3:0] A;

input[3:0] B;

output[3:0] Y;

assign Y=~(A&B);

endmodule

//------testbench of nand_gate--

module nand_gate_4bits_tb;

reg[3:0] aa,bb; //输入定义为reg

wire[3:0] yy;

nand_gate_4bits nand_gate_4bits(

.A(aa),

.B(bb),

.Y(yy)

);

initial begin

aa<=4'b0000;bb<=4'b1111; //用箭头等号对应实际电路

#10 aa<=4'b1110;bb<=4'b0011;

#10 aa<=4'b0110;bb<=4'b0111;

#10 aa<=4'b0111;bb<=4'b1110;

#10 aa<=4'b1101;bb<=4'b1111;

#10 $stop;

end

endmodule