理论:

![图片[1] - 【8】Verilog练习-串口数据发送 - 我的学记|刘航宇的博客 图片[1] - 【8】Verilog练习-串口数据发送 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/62b005a709475431299b8e15.jpg)

![图片[2] - 【8】Verilog练习-串口数据发送 - 我的学记|刘航宇的博客 图片[2] - 【8】Verilog练习-串口数据发送 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/62b006eb09475431299d4ab5.jpg)

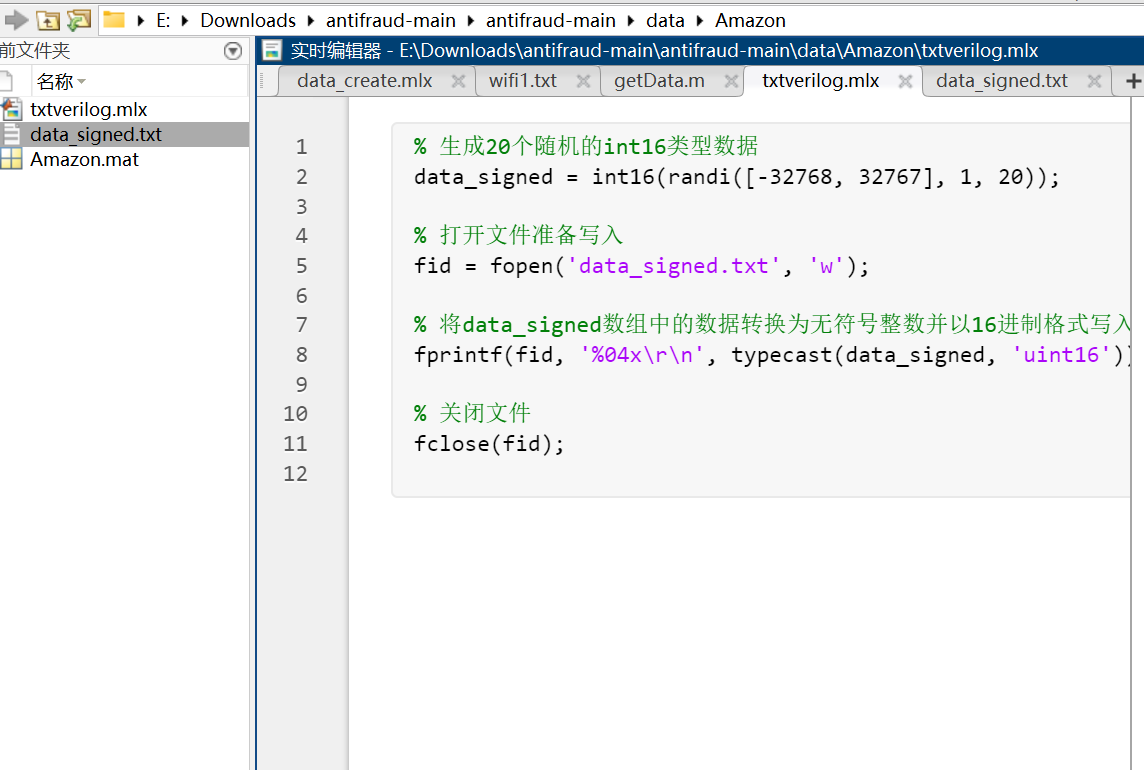

代码:

//串口发送模块

`timescale 1ns/10ps

module UART_TXer(

clk,

res,

data_in,

en_data_in,

TX,

rdy

);

input clk;

input res;

input[7:0] data_in;//准备发送的数据;

input en_data_in;//发送使能;

output TX;//输出使能

output rdy;//空闲标志,0表示空闲;

reg[3:0] state;//主状态机寄存器;

reg[9:0] send_buf;//发送寄存器

assign TX=send_buf[0];//连接TX;

reg[9:0] send_flag;//用于判断右移结束;

reg[12:0] con;//用于计算波特周期

reg rdy;

always@(posedge clk or negedge res)

if(~res)begin

state<=0;send_buf<=1;con<=0;send_flag<=10'b10_0000_0000;rdy<=0;

end

else begin

case(state)

0://等待使能信号;

begin

if(en_data_in)begin

send_buf={1'b1,data_in,1'b0};

send_flag<=10'b10_0000_0000;

rdy<=1;

state<=1;

end

end

1://串口发送,寄存器右移;

begin

if(con==5000-1)begin

con<=0;

end

else begin

con<=con+1;

end

if(con==5000-1)begin

send_buf[8:0]<=send_buf[9:1];

send_flag[8:0]<=send_flag[9:1];

end

if(send_flag[0])begin

rdy<=0;

state<=0;

end

end

endcase

end

endmodule

//----testbench of UART_TXer---

module UART_TXer_tb;

reg clk,res;

reg[7:0] data_in;

reg en_data_in;

wire TX;

wire rdy;

UART_TXer UART_TXer( //同名例化;

clk,

res,

data_in,

en_data_in,

TX,

rdy

);

initial begin

clk<=0;res<=0;data_in<=8'h7f;en_data_in<=0;

#17 res<=1;

#30 en_data_in<=1;

#10 en_data_in<=0;

#10000 $stop;

end

always #5 clk<=~clk;

endmodule结果:

![图片[3] - 【8】Verilog练习-串口数据发送 - 我的学记|刘航宇的博客 图片[3] - 【8】Verilog练习-串口数据发送 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/62b1922209475431299b3ded.jpg)