IC的设计过程可分为两个部分,前端设计(也称逻辑设计)和后端设计(也称物理设计)并没有统一严格的界限,涉及到与工艺有关的设计就是后端设计。

数字IC设计流程

1. 规格制定

芯片规格,也就像功能列表一样,是客户向芯片设计公司(称为Fabless,无晶圆设计公司)提出的设计要求,包括芯片需要达到的具体功能和性能方面的要求。

2. 详细设计

Fabless根据客户提出的规格要求,拿出设计解决方案和具体实现架构,划分模块功能。目前架构的验证一般基于SystemC语言,对构架模型的仿真可以使用SystemC的仿真工具。其中典型的例子是Synopsys公司的CoCentric和Summit公司的Visual Elite等。

3. HDL编码

使用硬件描述语言(VHDL,Verilog HDL,业界公司一般都是使用后者)将模块功能以代码来描述实现,也就是将实际的硬件电路功能通过HDL语言描述出来,形成RTL(寄存器传输级)代码。

设计输入工具:具有强大的文本编辑功能,多种输入方法(VHDL,Verilog,状态转移图,模块图等),语法模板,语法检查,自动生产代码和文档等功能。如Active-HDL,VisualVHDL/Verilog等。

RTL分析检查工具:Synopsys LEDA

4. 仿真验证

仿真验证就是检验编码设计的正确性,检验的标准就是第一步制定的规格。看设计是否精确地满足了规格中的所有要求。规格是设计正确与否的黄金标准,一切违反,不符合规格要求的,就需要重新修改设计和编码。

设计和仿真验证是反复迭代的过程,直到验证结果显示完全符合规格标准。

仿真验证工具Synopsys的VCS,Mentor ModelSim,Cadence Verilog-XL,Cadence NC-Verilog。

5. 逻辑综合――Design Compiler

仿真验证通过,进行逻辑综合。逻辑综合的结果就是把设计实现的HDL代码翻译成门级网表netlist。综合需要设定约束条件,就是你希望综合出来的电路在面积,时序等目标参数上达到的标准。逻辑综合需要基于特定的综合库,不同的库中,门电路基本标准单元(standard cell)的面积,时序参数是不一样的。所以,选用的综合库不一样,综合出来的电路在时序,面积上是有差异的。

一般来说,综合完成后需要再次做仿真验证(这个也称为后仿真,之前的称为前仿真)逻辑综合工具Synopsys的Design Compiler(DC),Cadence的 PKS,Synplicity的Synplify等。另外,和综合工具配合使用的还有很多其他工具,如静态时间分析工具,等效性检查工具等等。Synopsys公司和Cadence公司都提供完整的工具包。

5.1. STA

Static Timing Analysis(STA),静态时序分析,这也属于验证范畴,它主要是在时序上对电路进行验证,检查电路是否存在建立时间(setup time)和保持时间(hold time)的违例(violation)。这个是数字电路基础知识,一个寄存器出现这两个时序违例时,是没有办法正确采样数据和输出数据的,所以以寄存器为基础的数字芯片功能肯定会出现问题。STA工具有Synopsys的Prime Time。

5.2. 形式验证

这也是验证范畴,它是从功能上(STA是时序上)对综合后的网表进行验证。常用的就是等价性检查(Equivalence Check)方法,以功能验证后的HDL设计为参考,对比综合后的网表功能,他们是否在功能上存在等价性。这样做是为了保证在逻辑综合过程中没有改变原先HDL描述的电路功能。形式验证工具有Synopsys的Formality。前端设计的流程暂时写到这里。从设计程度上来讲,前端设计的结果就是得到了芯片的门级网表电路。

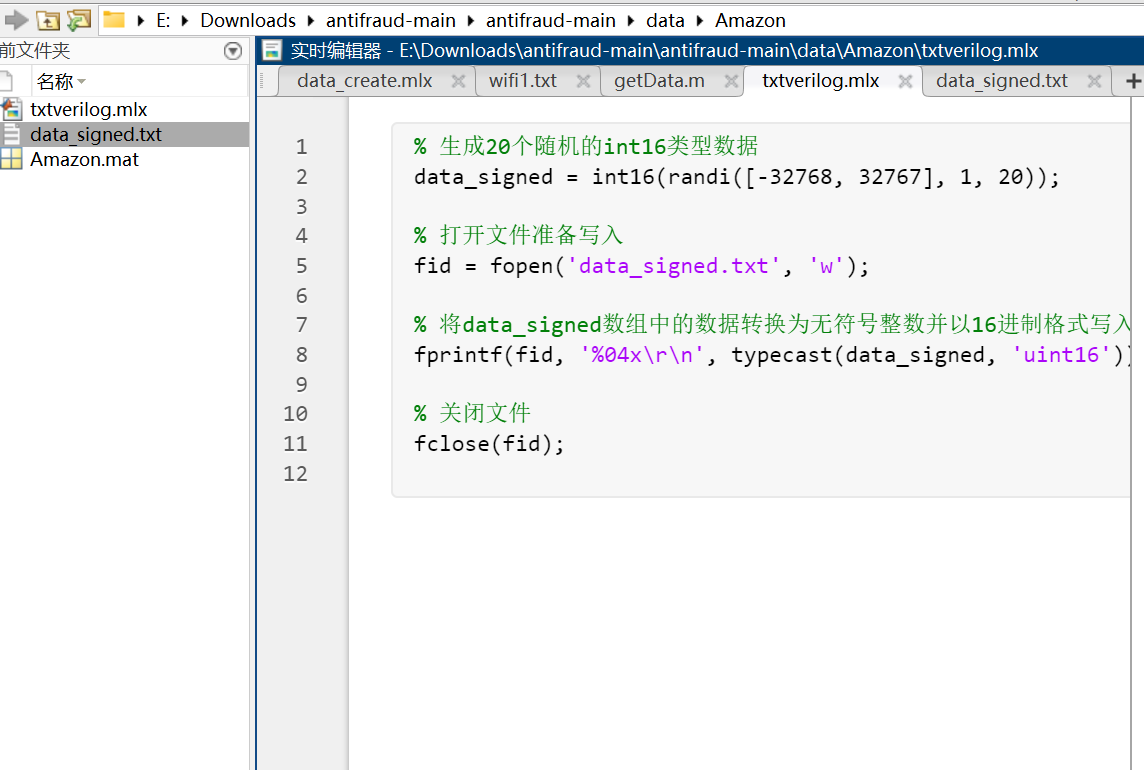

技能图解

![图片[1] - 【IC设计】数字IC设计流程及学习指南 - 我的学记|刘航宇的博客 图片[1] - 【IC设计】数字IC设计流程及学习指南 - 我的学记|刘航宇的博客](http://mianbaoban-assets.oss-cn-shenzhen.aliyuncs.com/xinyu-images/MBXY-CR-988b9d47a5cfdc06bacb37d7a3f8035f.png)

1.语言

主流的Verilog、VHDL

Verilog语言与软件语言最大的区别就是,因为它是用于描述电路的,因此它的写法是非常固定的,因为电路的变化是非常有限的。学习Verilog的时候,很多时候我们并不是在学习这门语言本身,而是学习其对应的电路特征,以及如何对这个电路进行描述。如果心中没有电路,那么你是不可能写好Verilog的。

VHDL语言的严谨性比Verilog要好,不像Verilog中一样存在大量符合语法却永远无法综合的语句。

SpinalHDL、Myhdl等

SpinalHDL和Chisel师承一脉,都是基于Scala来进行电路描述。其本质上仍旧是HDL而非HLS,在设计之前依旧需要有清晰的电路结构,只不过是在电路描述上更加方便和快捷而已。

目前有一些公司已经应用于FPGA设计中,ASIC应用还有待探究。

SpinalHDL资料:

https://spinalhdl.github.io/SpinalDoc-RTD/master/index.html

SystemVerilog/SystemC :

这两种语言都是为了验证而存在的,掌握基本的验证方法学有助于提高自己的debug效率,SystemVerilog是一种面向对象的语言,其设计的本意是用于搭建验证平台,主流的UVM方法也都是基于SystemVerilog实现的,所以立志成为IC验证工程师的同学,SystemVerilog的深入学习和流行方法论的学习都是必不可少的。

而对于那些只想做IC设计的同学而言,SystemVerilog同样也是值得学习的。且不说本文前面提到的用于提高验证效率的debug方法,即使只是为了做好设计,SystemVerilog也是大有用武之地。很多顶级的IC设计公司内部都开始使用SystemVerilog进行RTL设计了。

由于在SystemVerilog中加入了很多类似always_ff、always_comb等用于显式表明综合电路意图的新语法,代码的可读性更高,综合过程中也减少了歧义,尽可能地保证了综合结果与设计意图的一致性。从另一个角度来说,assertion的加入也极大地提高了代码的debug效率,非常有助于在大规模的数据交互过程中定位到出错的初始点,没有掌握的同学可以多花一些时间学习一下。

-> SV基础知识

脚本语言:Makefile/Perl/Python/Shell

Makefile/Perl/Python/Shell都是常用的脚本语言,进行批量修改文本内容,实现自动化操作等,掌握一门得心应手的脚本语言将对工作效率的提升帮助极大。但凡做过一次的事情,就没有必要重复第二次。

-> Perl在IC中的应用

脚本语言:Tcl

在IC设计这个领域中,Tcl是一门非常常见的语言。可以用于描述时序和管脚约束文件,UPF信息,也可以用来搭建简单的工作平台。既是很多EDA工具默认支持的脚本语言,也是这些工具配置和输出的文件格式。因此,能够读懂Tcl,掌握Tcl语言的基本语法,就可以帮助更好的使用EDA工具。

-> 从零开始学Tcl

C语言

作为基础语言,在验证时,往往需要用到C写的case;

2.基础知识

数电模电、电路分析、数据结构、计算机体系架构等

AMBA总线

AXI、AHB、APB、CHI、ACE等;

-> AMBA总线

高低速接口

PCIE、DMA、DDR、USB、UART、SPI、I2C、MIPI等

-> 总线接口

低功耗设计

动态功耗、静态功耗、常见低功耗设计方法

-> 低功耗设计

静态时序分析

建立时间、保持时间、亚稳态及其解决方法、时序约束

-> 时序约束策略 、亚稳态、 FPGA中的亚稳态

设计方法

乒乓操作、流水线、串并转换、无毛刺切换、状态机等

跨时钟处理:快到慢、慢到快、异步FIFO(FIFO深度计算)等

->时钟切换电路(Glitch-free clock switching circuit)、异步FIFO、同步FIFO、同步和异步FIFO、FIFO深度计算

3.设计工具

linux系统:linux、shell常见命令

gvim/emac编辑器:

熟练使用Vim/Emacs,用编程的方式来编程,可以提高效率。

版本管理工具:SVN、Git、p4等

版本管理,简而言之,就是一种用于记录和查询文件版本改动的工具;

EDA工具

仿真工具:NCVerilog/ VCS/ ModelSim/ iVerilog

以上是比较业界比较主流的仿真工具,其中Icarus Verilog (iVerilog)为开源工具,仿真过程需要了解:

如何指定编译的文件类型;

如何指定编译文件清单;

如何指定索引目录;

如何指定仿真精度;

如何指定临时的宏变量;

如何指定语法检查的严苛等级;

如何混合编译由多种语言写成的工程;

如何调用不同波形生成工具的pli接口;

如何配合SDF反标进行后仿等;

-> 芯片后仿及SDF反标、VCS实用技巧、开源verilog仿真工具iverilog+GTKWave

波形查看工具:DVE/ Verdi/ gtkWave

以上是业界比较主流的波形查看工具,所有的波形查看器都必须支持标准波形文件.vcd格式,但是由于.vcd格式的存储性能并不好,冗余信息过多,所以各波形查看工具都纷纷推出了自己支持的波形文件格式,如DVE的.vpd,Verdi的.fsdb,ModelSim的*.wlf;

gtkWave也是跨平台的,而且简单易用,支持.vcd标准格式,同时支持高性能压缩格式.lxt和*.fst,gtkWave自带vcd转fst的转换器;

通常几G左右的.vcd格式波形转换为.vpd格式后只有几十MB左右,而转换为.fsdb后通常会更小,因此将标准波形文件.vcd转换为其他压缩格式更加有利于数据备份。

-> fsdb实用技巧、verdi实用技巧

逻辑等效性检查工具:formality-> 形式验证与formality基本流程

从功能上对综合后的网表进行验证,常用的就是等价性检查方法,以功能验证后的HDL设计为参考,对比综合后的网表功能,他们是否在功能上存在等价性。这样做是为了保证在逻辑综合过程中没有改变原先HDL描述的电路功能。

综合工具:dc ->DC综合

逻辑综合就是将HDL代码翻译成门级网表netlist;

lint/cdc检查工具:spyglass -> SpyGlass安装教程、spyglass 基础操作、spyglass 常见错误lint

后端:PT、IIC2、innovus等

FPGA综合布线布局工具:synplify/vivado->

->synplify 基础操作、基于synplify+vivado生成bitfile

其他:VC_static_tools ->VC_static Tools安装教程

4.相关岗位

前端设计

RTL IP设计:从算法协议到RTL coding的能力;

SoC设计集成/验证:总线、功耗、系统架构的能力;

SOC侧重将IP,模块集成形成一个系统,所以片上互联总线和外设接口是掌握的重点。片内互联总线一般是AMBA总线。外设接口又分为低速接口和高速接口,其中低速接口包括I2C,UART,SPI等,高速接口包括SATA,USB,PCIE,DDR等;

验证

FPGA原型验证:HAPS -> HAPS®-100原型系统、芯片验证技术 |HAPS与高性能ASIC原型验证

UVM验证:SV、UVM主流验证方法学 ->UVM芯片验证

EMU验证:zebu、帕拉丁 -> 芯片验证应用|基于ZeBu平台的虚拟主机应用方案

综合:

逻辑综合就是将HDL代码翻译成门级网表netlist;

STA

Static Timing Analysis(STA),静态时序分析,它主要是在时序上对电路进行验证,检查电路是否存在建立时间(setup time)和保持时间(hold time)的违例(violation),一个寄存器出现这两个时序违例时,是没有办法正确采样数据和输出数据的,所以以寄存器为基础的数字芯片功能肯定会出现问题。

DFT

Design ForTest,可测性设计。芯片内部往往都自带测试电路,DFT的目的就是在设计的时候就考虑将来的测试。DFT的常见方法就是,在设计中插入扫描链,将非扫描单元(如寄存器)变为扫描单元;如bist、Scan Design、JTAG、ATPG等;

后端

物理验证、布线布局、静态时序分析、等价性检查、功耗分析