前言

在微处理器芯片中,乘法器是进行数字信号处理的核心,同时也是微处理器中进行数据处理的关键部件。乘法器完成一次操作的周期基本上决定了微处理器的主频。乘法器的速度和面积优化对于整个CPU的性能来说是非常重要的。为了加快乘法器的执行速度,减少乘法器的面积,有必要对乘法器的算法、结构及电路的具体实现做深入的研究。

视频课程,关注本人B站账号有完整版前端中端设计教程

1. 设计内容

完成一个全定制的 8x8 bits 基-4 Booth 编码码乘法器核心电路设计,即可以不考虑输入、输出数据的寄存。

2. 设计目标

本设计最主要的目标是在电路速度尽可能高的条件下最小化电路的功率-延迟积(PDP)。所以首先在电路结构设计完成后需要分析、考虑最长延迟路径。根据设计目标进行逻辑链优化。

3.原理介绍

本乘法器采用基4booth编码,输入为两个8位有符号数,输出为16位有符号数。基4的booth编码将两个8位有符号数计算成4个部分积。4个部分积经过一层4-2压缩器得到2个部分积,得到两个部分积,两个部分积进过一个超前进位加法器(cla)得到最终结果。![图片[1] - VLSI设计-基4 Booth乘法器前端与中端实现 - 我的学记|刘航宇的博客 图片[1] - VLSI设计-基4 Booth乘法器前端与中端实现 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63d65f48face21e9efea3600.jpg)

思维扩展:

若输入为两个128位有符号数,输出为256位有符号数。基4的booth编码将两个128位有符号数计算成64个部分积。64个部分积经过一层4-2压缩器得到32个部分积……在经过几层4-2压缩器,最终得到两个部分积,两个部分积进过一个超前进位加法器(cla)得到最终结果。结构框图如下:![图片[2] - VLSI设计-基4 Booth乘法器前端与中端实现 - 我的学记|刘航宇的博客 图片[2] - VLSI设计-基4 Booth乘法器前端与中端实现 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63d664efface21e9eff63343.jpg)

4.电路&Verilog代码

基4Booth编码器

对于被乘数b_i进行编码,Booth 基-4 编码是根据相邻 3 位为一组,前后相邻分组重叠一比特位,从低位到高位逐次进行,在乘数的最右边另增加一位辅助位 0,作为分组的最低位。Booth 4-基编码的优点是可以减少 Booth 2-基产生部分积的一半,Booth 基-4 除了具有高速特性还具有低功耗的特点。![图片[3] - VLSI设计-基4 Booth乘法器前端与中端实现 - 我的学记|刘航宇的博客 图片[3] - VLSI设计-基4 Booth乘法器前端与中端实现 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63d65ff8face21e9efebbdec.jpg)

对应case

case(b_i)

3'b000 : booth_o <= 0;

3'b001 : booth_o <= { a_i[length-1], a_i};

3'b010 : booth_o <= { a_i[length-1], a_i};

3'b011 : booth_o <= a_i<<1;

3'b100 : booth_o <= -(a_i<<1);

3'b101 : booth_o <= -{a_i[length-1],a_i};

3'b110 : booth_o <= -{a_i[length-1],a_i};

3'b111 : booth_o <= 0;

default: booth_o <= 0;4-2压缩器

4-2 压缩器的原理图如下所示,把 4 个相同权值的二进制数两个权值高一级的二进制数和,它有 5 个输入端口:包括 4 个待压缩数据 a1、a2、a3、a4 和一个初始进位或低权值 4-2 压缩传递的进位值 Ci;3 个输出端口:包括一比特位溢出进位值 Co,进位数据 C,伪和 S。

下面代码得到的结果out1的权值高一位,下一层部分积计算时需要将out1的结果左移一位(out1<<1);![图片[4] - VLSI设计-基4 Booth乘法器前端与中端实现 - 我的学记|刘航宇的博客 图片[4] - VLSI设计-基4 Booth乘法器前端与中端实现 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63d6609aface21e9efed0f9a.jpg)

功能代码:

assign w1 = in1 ^ in2 ^ in3 ^ in4;

assign w2 = (in1 & in2) | (in3 & in4);

assign w3 = (in1 | in2) & (in3 | in4);

assign out2 = { w1[length*2-1] , w1} ^ {w3 , cin};

assign cout = w3[length*2-1];

assign out1 = ({ w1[length*2-1] , w1} & {w3 , cin}) | (( ~{w1[length*2-1] , w1}) & { w2[length*2-1] , w2});超前进位加法器

4位超前进位代码:

//carry generator

assign c[0] = cin;

assign c[1] = g[0] + ( c[0] & p[0] );

assign c[2] = g[1] + ( (g[0] + ( c[0] & p[0]) ) & p[1] );

assign c[3] = g[2] + ( (g[1] + ( (g[0] + (c[0] & p[0]) ) & p[1])) & p[2] );

assign c[4] = g[3] + ( (g[2] + ( (g[1] + ( (g[0] + (c[0] & p[0]) ) & p[1])) & p[2] )) & p[3]);

assign cout = c[width];代码下载

4、仿真分析

前端逻辑仿真

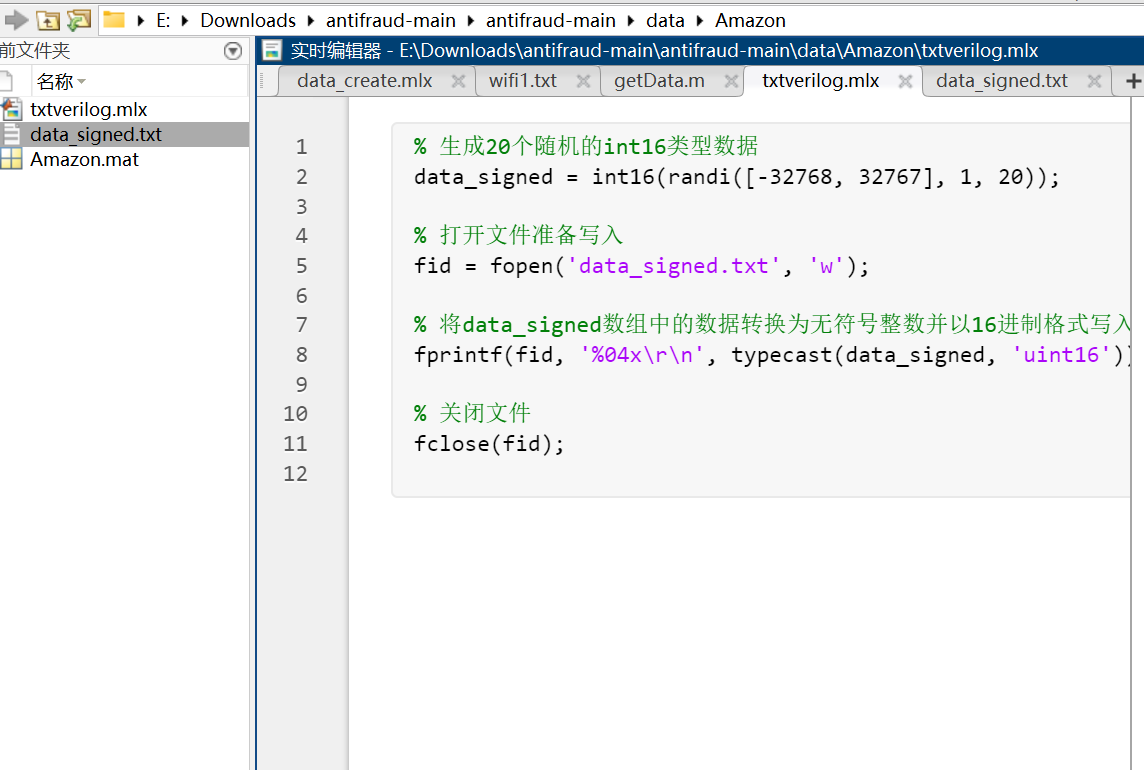

本设计是单纯的组合逻辑,由仿真结果可知有符号乘法设计结果完全正确。![图片[5] - VLSI设计-基4 Booth乘法器前端与中端实现 - 我的学记|刘航宇的博客 图片[5] - VLSI设计-基4 Booth乘法器前端与中端实现 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63d66417face21e9eff46b47.jpg)

电路与性能仿真

电路图

![图片[6] - VLSI设计-基4 Booth乘法器前端与中端实现 - 我的学记|刘航宇的博客 图片[6] - VLSI设计-基4 Booth乘法器前端与中端实现 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63d66449face21e9eff4cfd1.jpg)

面积报告

DC综合后,总共的单元面积为7853.630484等效门,总面积为78273.983938等效门。![图片[7] - VLSI设计-基4 Booth乘法器前端与中端实现 - 我的学记|刘航宇的博客 图片[7] - VLSI设计-基4 Booth乘法器前端与中端实现 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63d66475face21e9eff5292b.jpg)

功耗报告

![图片[8] - VLSI设计-基4 Booth乘法器前端与中端实现 - 我的学记|刘航宇的博客 图片[8] - VLSI设计-基4 Booth乘法器前端与中端实现 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63d66497face21e9eff576a6.jpg)

由于该电路是完全的组合逻辑,无CLK端口,因此未作时序约束。

后端

做到这里完成了前端中端设计任务,在流片前还需要完成后端设计及验证。由于本电路规模大,我们可以利用EDA如(SOCE或者ICC)完成版图布局,由于时间仓促,笔者暂未更新后端教程。