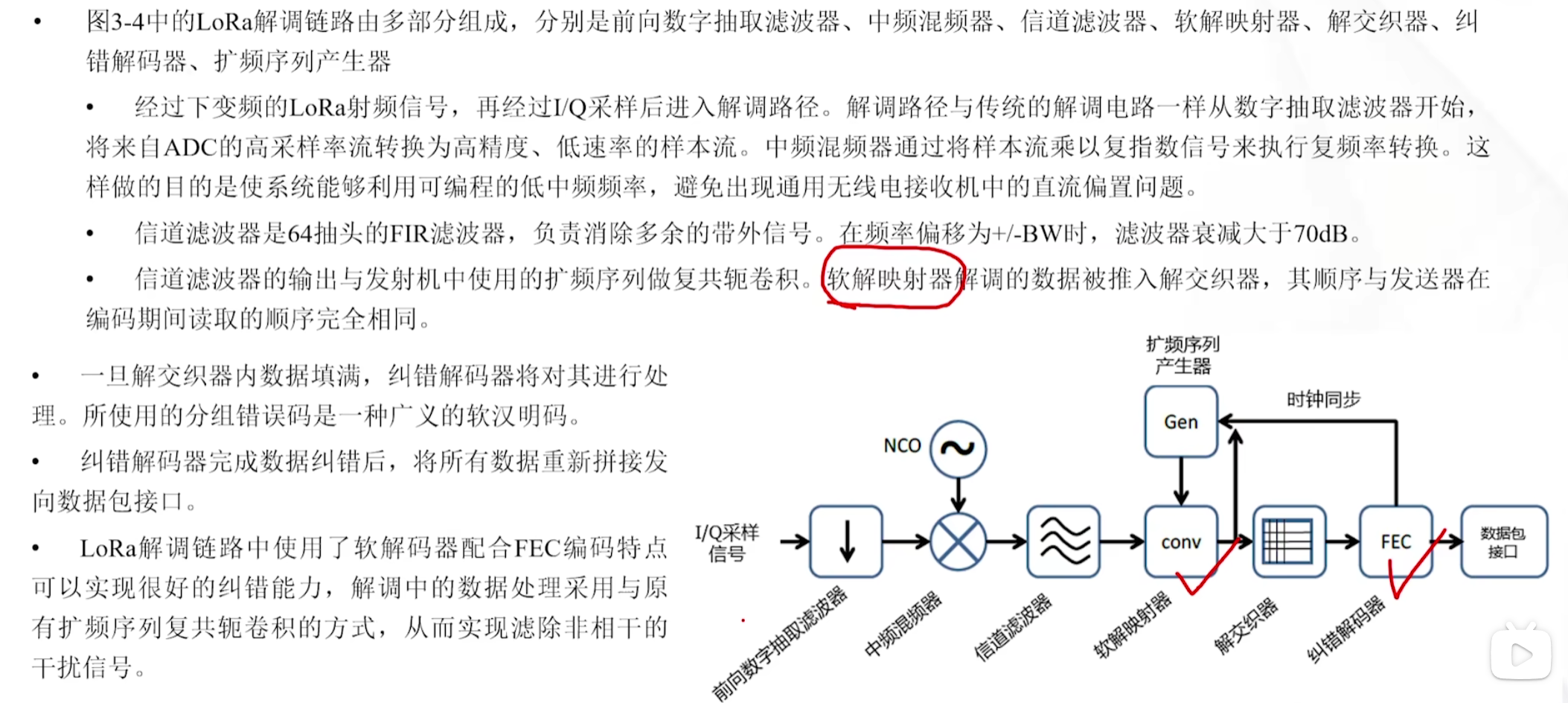

LoRa调制链路

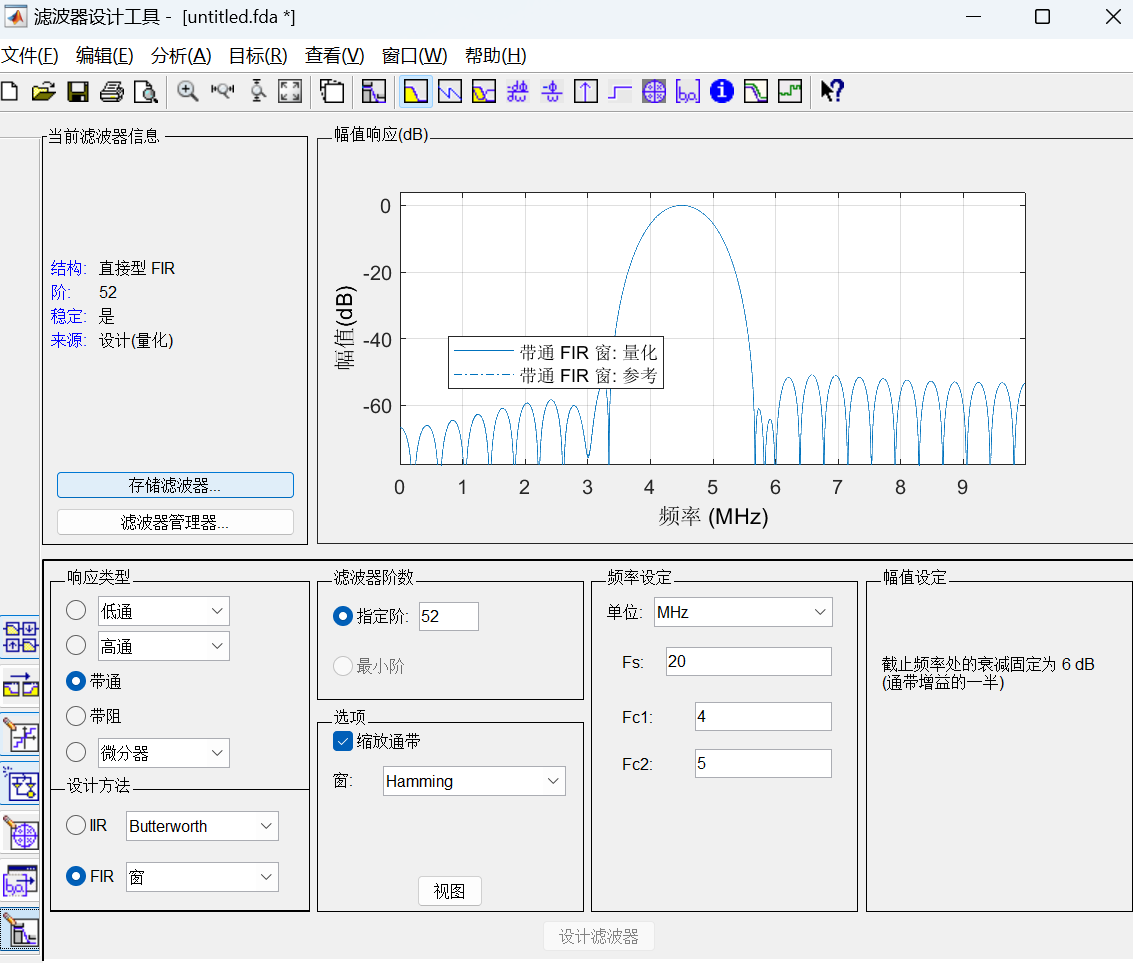

●LoRa调制链路由五部分组成,分别是纠错编码机、交织器、扩频序列产生器、笛卡

尔极坐标转换器、Delta-sigma调制器。

纠错编码器

●当一组数据(用户的有效载荷(Payload) )被推入数据包接口( Packet Interface)时,调制过程开始。调制器通过纠错编码机将前向纠错编码(ForwardErrorCorrection,FEC)添加到这些字节中。

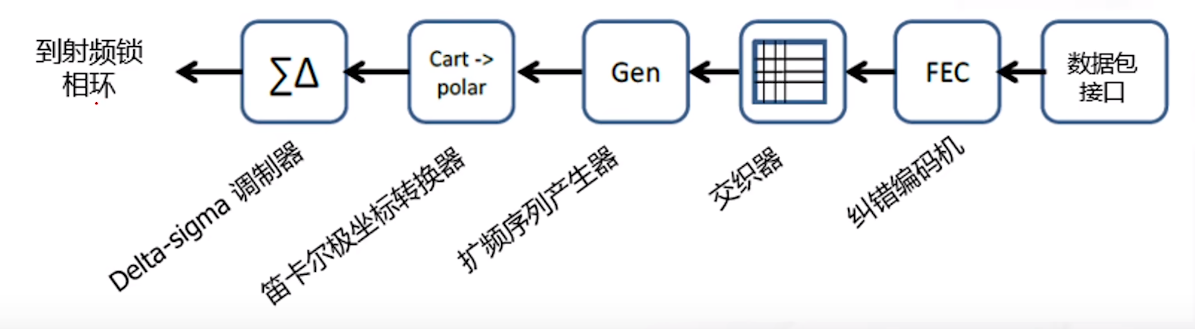

●这些有效载荷数据每个字节首先分成半字节(4比特一组)。然后,根据编码速率配置,

在1到4冗余纠错位之间选择并追加到每个半字节。调制器编码速率通过CR寄存器进行设置,表3-1为前向纠错编码配置表。

交织器

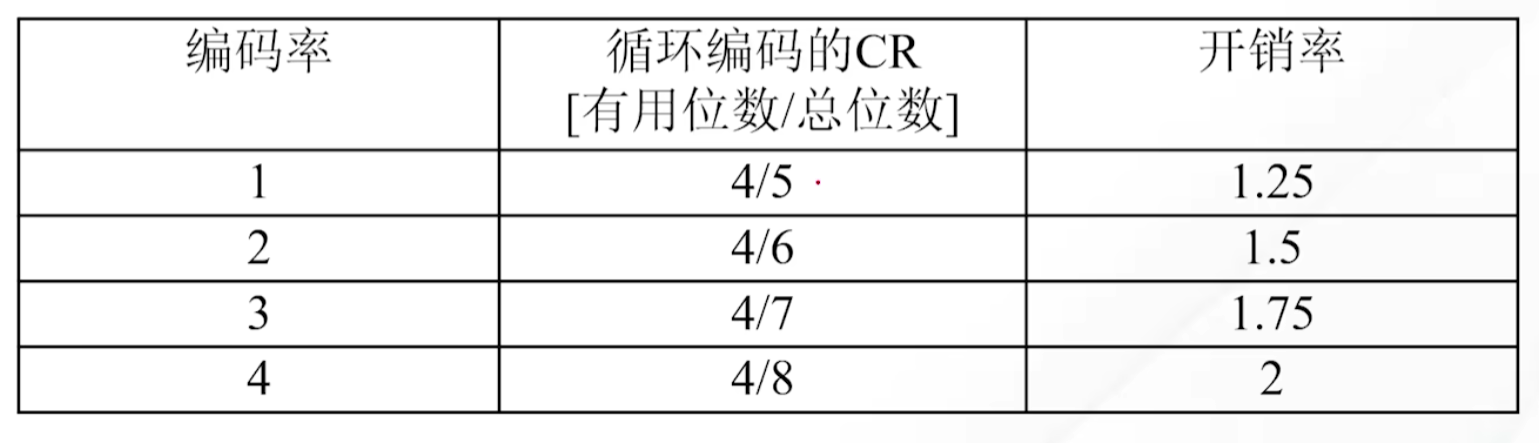

●纠错编码后,产生的(4+CR)位比特段,随后被存储到交织器的存储阵列中。交织器(Interleaver) 有(4+CR)列和SF行。一旦交织器满了,它的内容将编码到码元上。每个码元都带有SF位。因此,交织器内有(4+CR) *SF 比特,独立于扩频因子SF被编码到4+CR码元上。

●这里举一一个例子让读者理解交织器。假设此时CR=1,,, SF=7, 其交织器为7行、5列。需要传输的数据流为:00000001001000110100010101100111。先将这些比特流分为4b一组(b1,b2,b3,b4) : 0000; 0001; 0010; 0011; 0100;0101; 0110; 0111; 对上述数据增加1比特校验位(b1,b2,b3,b4,C) 后为: 00000; 00011; 00101; 00110; 01001;01010; 01100; 01111; 再将,上述数字填入交织器的存储列阵中,当35b数据进入交织器的存储列阵后,交织器存储满了,下一组数据(b1,b2,b3,b3,C) 需要填入下一个交织器中。

扩频序列产生器

门坐标转换、Delta-sigma调制输出

解调

编码

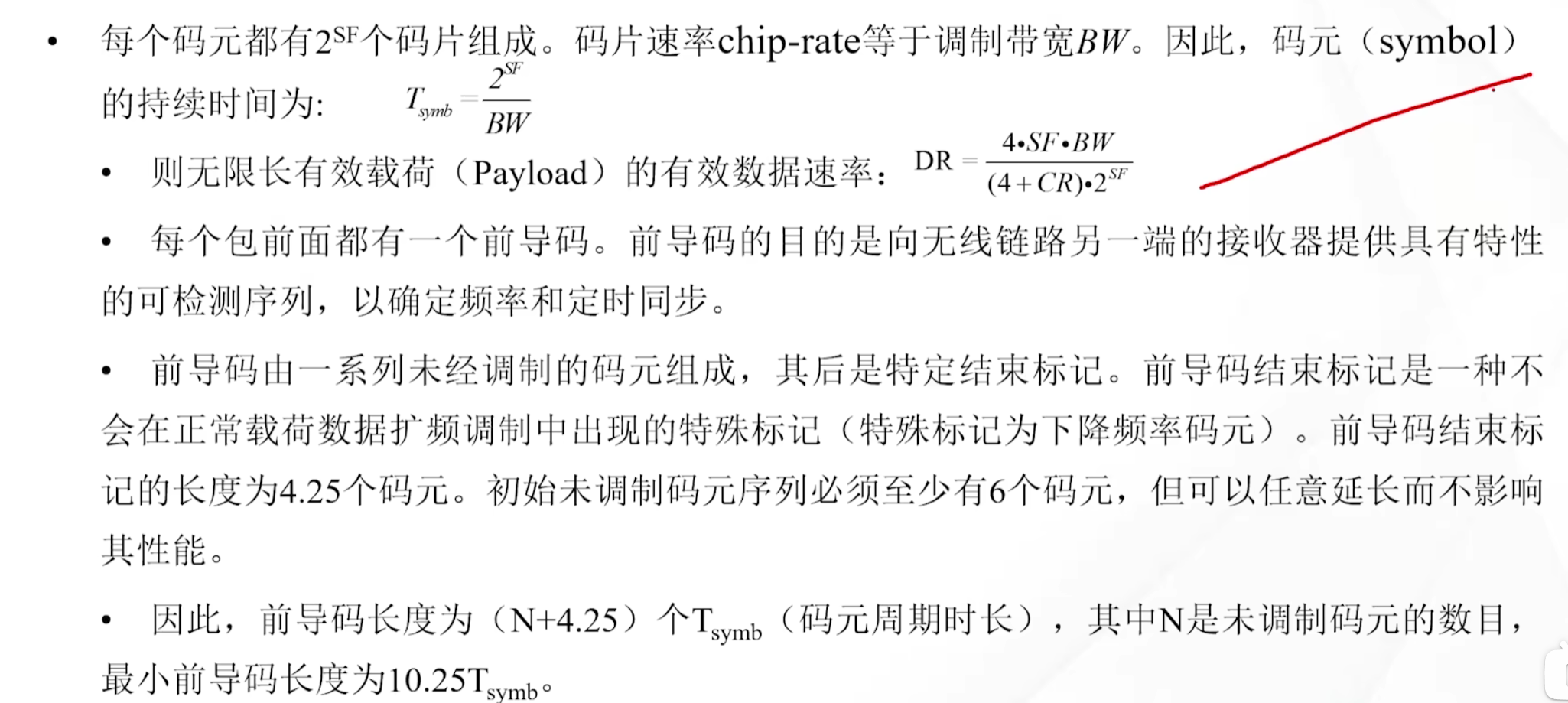

下是一个SF=7的LoRa调制编码图, 从图中可以看出码元、码片、比特速率、载荷数据之间的关系。

图中SF=7, 所以发送信号带宽切分为128(27-128)个频率段的码片。假设该系统工作频率为470MHz,BW=250kHz,相邻码片间隔为250kHz/128=1 .95kHz,此时f0=470MHz,f1=470.00195MHz,f2=470.0039MHz,.. .f127=470.24805MHz.

图3-9中有三个时间长度分别是码片率(Chip rate),比特速率(Data rate),码元率(Symbol rate),可以清楚地看出它们的对应关系.![图片[1] - LoRa码元调制、编码与解调 - 我的学记|刘航宇的博客 图片[1] - LoRa码元调制、编码与解调 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63afa56808b683016354909c.jpg)

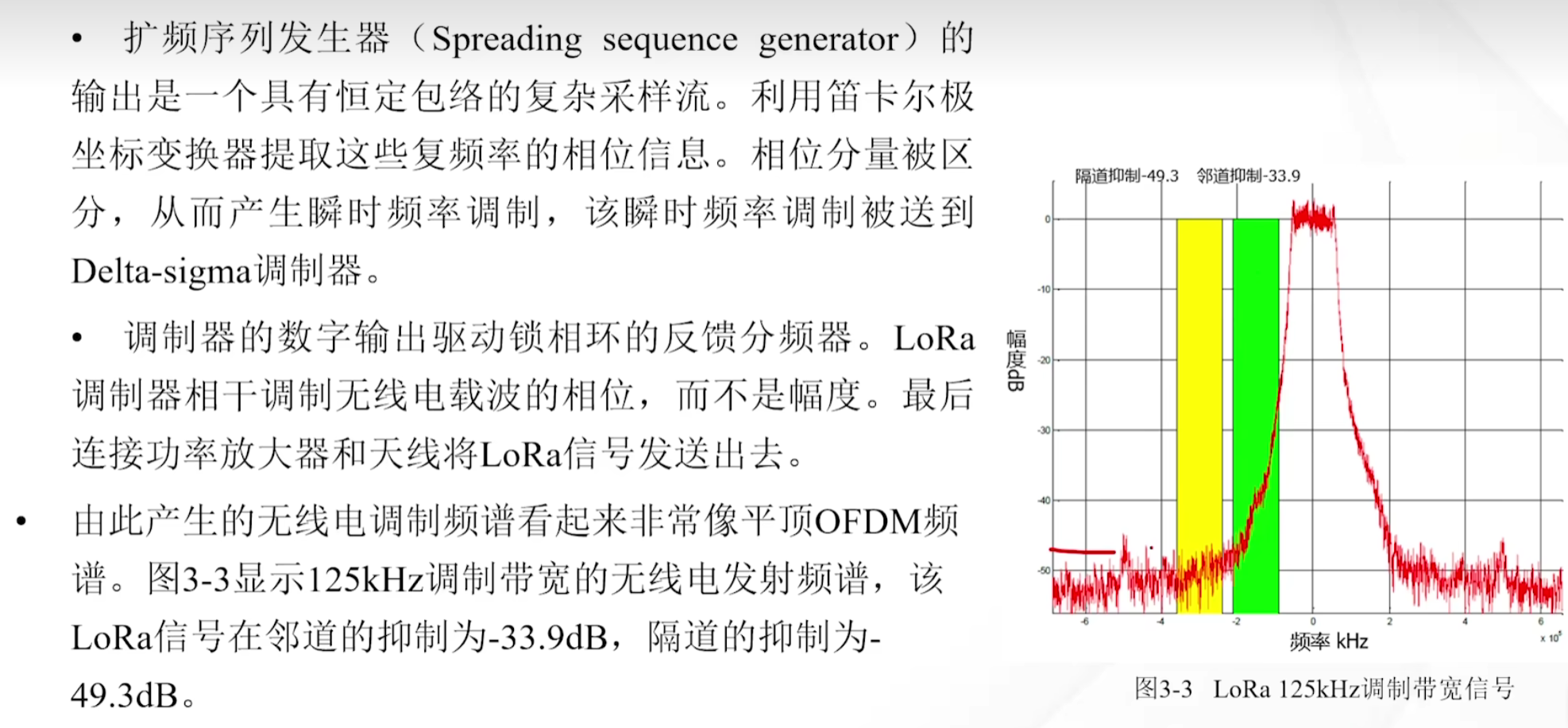

不同的SF对应带宽BW除以时间的斜率,SF越大倾斜角度越小。SF和BW对应一种LoRa调制方式,只有接收机也采用对应的SF和BW才能正常解调,否则信号在相干解

调中会淹没在噪声中。在实际的相干解调中,LoRa调制在不同的SF信号或不同的BW下都是正交的,频带可以充分利用。比如在BW=125kHz的同频段内,一个SF=7信号

Psez和一个SF=8信号Psps都在发射,频段内的噪声为N,,当两个信号都满足解调信噪比要求时(SNRsf7 >=-7.5dB; SNRsf8>=-10dB) ,两个信号都可以正常解调。这里需要注意,当计算SNRsf7时,SF=8的信号表现为此系统噪声,SNRsF7= Psp/(N0+Psf8) ;

同理当计算SNRsf8时,SF=7的信号表现为此系统噪声,SNRsf8=Psf8/(N0+Psf7).![图片[2] - LoRa码元调制、编码与解调 - 我的学记|刘航宇的博客 图片[2] - LoRa码元调制、编码与解调 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63afa92f08b6830163588ffb.jpg)