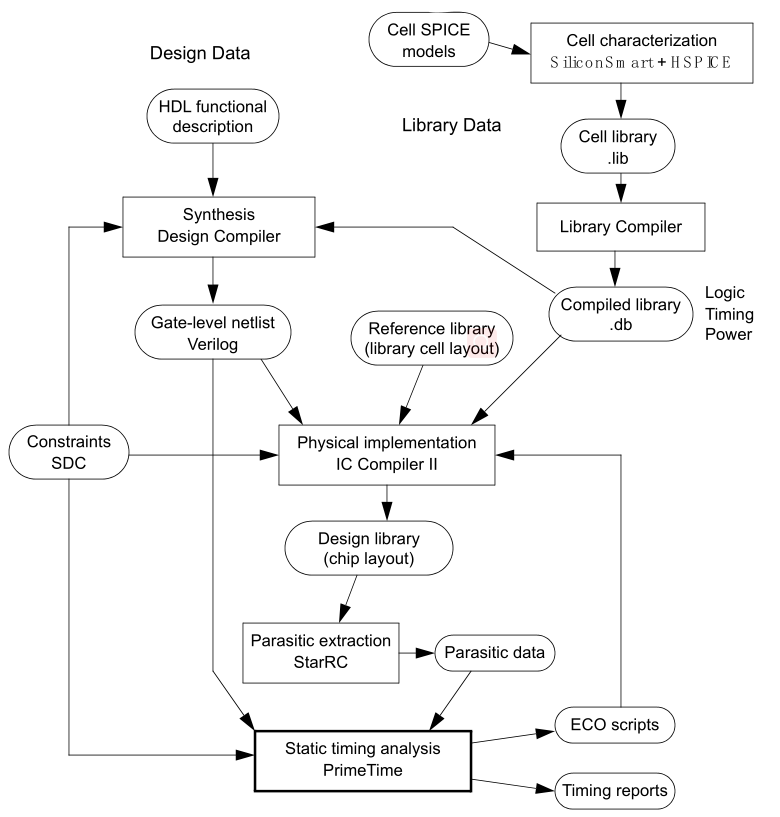

Design Compile是synopsys的综合软件,它的功能是把RTL级的代码转化为门级网表。综合包括转译(Translation),优化(Opitimization),映射(Mapping)三个过程。在转译的过程中,软件自动将源代码翻译成每条语句所对应的功能模块以及模块之间的拓扑结构,这一过程是在综合器内部生成电路的布尔函数的表达,不做任何的逻辑重组和优化。优化:基于所施加的一定时序和面积的约束条件,综合器按照一定的算法对转译结果作逻辑优化和重组。在映射过程中,根据所施加的一定的时序和面积的约束条件,综合器从目标工艺库中搜索符合条件的单元来构成实际电路。![图片[1] - Design Compile(DC)使用简版 - 我的学记|刘航宇的博客 图片[1] - Design Compile(DC)使用简版 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63c2c592be43e0d30ecc79fb.jpg)

DC 又称为设计综合 将设计的RTL代码综合成门级网表的过程。

在 DC 流程中 一般要经过以下几个步骤,以项目A为例 做如下分析:

1】 在项目子目录下创建DC文件夹,在DC文件夹下分别创建db in lib_syn log netlist

rpt和 script 文件夹 以及一个makefile 文件用来运行DC 脚本 。

2】 第二步就是复制相应工艺技术库文件到lib_syn ,一般有2种文件各3个分别包括了typical worst 和 best情况,一类是db,文件一类是lib 文件 也可以在lc_shell 下读取lib 得到相应的db文件。

3】 第三步将需要综合的设计RTL代码(Verilog 文件)复制到in 文件夹

4】 第四步在script 创建综合脚本,脚本创建过程将在后面介绍

5】 第五步编写运行脚本的makefile 文件

6】 第六步运行脚本而后查看综合报告,是否有违例现象出现,如果有修改脚本加以修复直到最终通过设计。

注意 另外的几个文件夹作用 db文件夹存放DC综合生成的项目db文件,综合网表输出到netlist 文件夹,综合程序运行报告存放在log文件夹中,而综合结果的数据报告则存放在rpt 文件夹中。

DC脚本的编写(A.scr)

DC综合脚本基本上有几大部分组成

1】定义综合环境中命名规则(分别对net cell port 命名)

define_name_rules verilog –casesensitive

define_name_rules verilog –type net –allowed “a-z A-Z 0-9 _ ” \

-first_restricted “ _ 0-9 N ” \

-replacement_char “_ ” \

-prefix “n”

define_name_rules verilog –type cell –allowed “a-z A-Z 0-9 _ ” \

-first_restricted “ _ 0-9 ” \

-replacement_char “_” \

-prefix “u”

define_name_rules verilog –type port –allowed “a-z A-Z 0-9 _ ” \

-first_restricted “ _ 0-9 ” \

-replacement_char “_” \

-prefix “p”2】综合环境的建立

指明库所在的位置

Search_path = { lib_syn/db }

指定综合所需目标库一般选用最恶劣情况worst 库作目标库

target_library = { slow.db}

创建链接库,链接库中包括了一些已经做好的设计和子模块,又包括了当前设计的目标库是设计实例化时所用的库文件

link_library = { “ * ” , slow.db } + synthetic_library

在上述的环境建立所需的各类库中,一般有生产商提供目标库,库中的各类cell用于逻辑映射,链接库则包括了目标库,还包括其他一些以前设计实例基本单元,我们门级网表实例化元件和单元都来自于它。

3】RTL 代码的读入

read –format verilog ./in/ Encoder_32k.v

read –format verilog ./in/ Encoder_DBLOCK.v

read –format verilog ./in/ Encoder.v

read –format verilog ./in/ Step_rom.v指明设计顶层

current_design = Encoder

展开设计分解原设计组

ungroup -all –flatten

设计唯一实例化

uniquify

4】综合环境约束

用户往往需要设置worst case 和 best case 的库来验证setup timing 修复 hold timing

不清楚命令使用和属性 可使用 man set_min_library 查看

set_min_library lib_syn/db/slow.db -min_version lib_syn/db/fast.db

编译操作条件的表述

set_operating_conditions -min slow –min_library slow \

-max fast –max_library fast 设置wire_load_model

wire_load_model 负载模型的每一种模型定义,它定义相关的net_length 和 net fanout 属性 而wire_load_mode 则不同指的是不同logic margin 连线net的处理方式 一般我们只设置前者

set_wire_load_model -name “ Silterra18_w110 ” –min

set_wire_load_model -name “ Silterra18_w110 ” –max设置模块输入驱动强度信息 man set_driving_cell 查看帮助

set_driving_cell -lib_cell BUFX1 –pin Y –library slow –dont_scale –no_design_rule all_input ( )5】设计时钟相关约束

create_clock clk -period 40

set_clock_latency 0.3 –rise { clk }

set_clock_latency 0.3 –fall { clk }

set_clock_uncertainty –setup 0.3 { clk }

set_clock_uncertainty –hold 0.3 { clk }6】禁止改变门电路控制结构

芯片中的时钟和复位电路一般由门电路控制的,我们不希望DC在综合时候改变它的结构以保证时钟信号和复位信号的稳定性和可靠性需要设置,禁止对某些单元进行优化

set_dont_touch_network { clk, rstn }

set_dont_touch { rstn }7】异步电路处理

任何跨越异步边界的路径我们都对其禁止时序分析

set_false_path -from { rstn } –to { clk }

8】设置其他可选约束和禁用单元

可选约束一般包括 set_max_fanout set_max_capacitance set_max_transition set_load 等 这些属性一般在技术库中已经设置了,只有技术库不能满足设计要求时才使用脚本增加约束选项

本脚本中只增加了

set_load 0.02 all_output ( )

Set_max_transition 2.5 current_design 输入输出直通buffer 插入,多重端口的连接插入buffer (选用)

set_fix_multiple_port_nets –feedthrough

输出端口插入buffer , 隔离端口 (必须)

set_isolate_ports –type buffer all_output ( )

9】检查设计层次关系进行单元映射

check_design –one_level

compile –map_effort medium10】修复hold时序 重新编译

set_fix_hold {clk }

compile –only_hold_time 11】导出编译综合相关报告

核对网表命名规则修改相关信息 change_names –rules verilog –hierarchy –verbose

检查整体设计导出报告

check_design > ./rpt/adpcm.rpt

移除未连接的相关端口

remove_unconnected_ports find ( hierarchy cell , “ * ”)

导出设计面积报告

report_area > ./rpt/adpcm_area.txt

导出设计违例报告

report_constraint –all_violators > ./rpt/adpcm_cons.txt

导出setup时序违例的详细报告

report_timing –nworst 50 > ./rpt/adpcm_max_time.txt

导出hold 时序违例的详细报告

report_timing -delay min –nworst 20 > ./rpt/adpcm_min_time.txt

导出综合的设计中cell和reg_cel的报告

report_cell > ./rpt/adpcm_cell.txt

report_cell {find (cell, “* _reg *”)} > ./rpt/adpcm_reg_cell.txt12】生成综合网表和pnr 所需的时序约束文件

write -hierarchy -output ./db/adpcm.db

write -format verilog –hierarchy -output ./netlist/adpcm.sv

write_sdf ./netlist/adpcm.sdf

write_sdc ./netlist/adpcm.sdc

exit13】compile-ultra![图片[2] - Design Compile(DC)使用简版 - 我的学记|刘航宇的博客 图片[2] - Design Compile(DC)使用简版 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63dbb958ac6ef8601607d6fb.jpg)