一、ICC综合概述

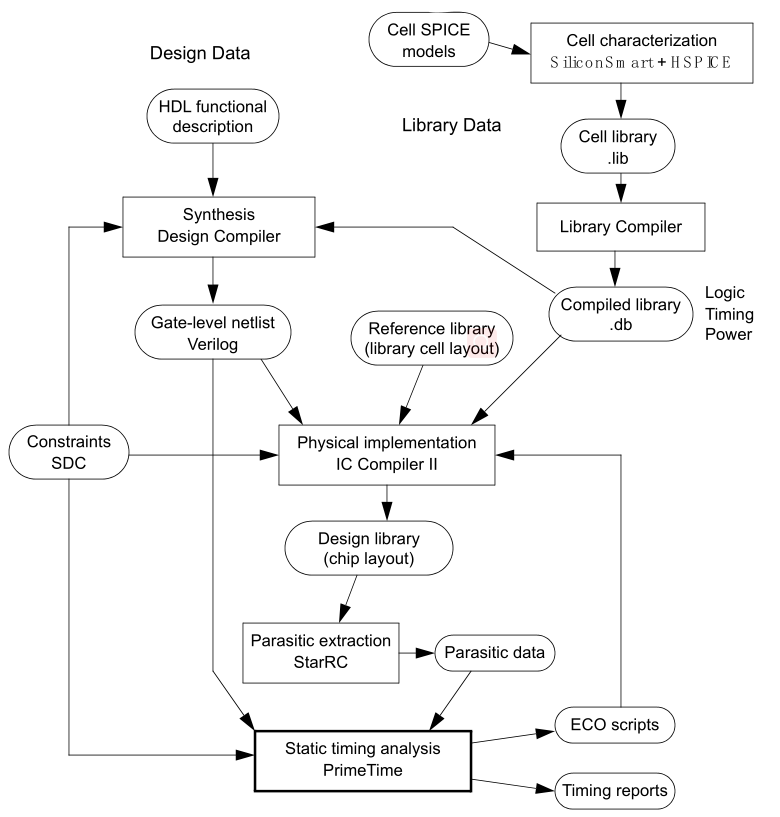

ICC(IC Compiler)是把门级网表转换成foundry厂可用于掩膜的版图信息的过程,它包括数据准备、布局、时钟树综合、布线等步骤。![图片[1] - Synopsys ICC简单教程 - 我的学记|刘航宇的博客 图片[1] - Synopsys ICC简单教程 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63d0e3ec588a5d166c56157b.jpg)

ICC输入文件

ICC输入需要两部分信息:综合数据+物理数据。

综合数据:

门级网表文件,如orca.v

约束文件,如orca.sdc

逻辑库文件,包含时序信息,如标准单元sc.db,宏单元macros.db,输入输出单元io.db等

物理数据:

技术文件,包含金属层等信息,如abc_6m.tf

线负载模型,TLU+

物理库文件,包含版图信息,如标准单元sc.mw,宏单元macros.mw,输入输出单元io.mw等

ICC输出文件

ICC输出的是GDSII格式的版图,用于流片。

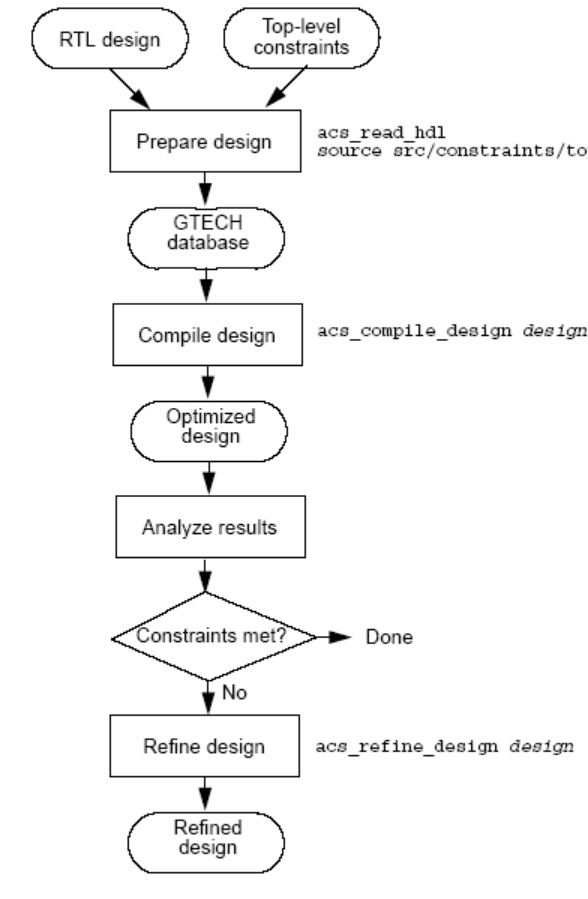

二、ICC综合流程

参考Synopsys ICC lab1的RISC_CHIP的例子,展示各个流程发生的变化。

1、逻辑库、技术库、版图库等基本参数设定

这是前期的准备工作,设定搜索路径、逻辑时序库.db、负载模型库.tluplus等。

2、创建自己的Milkyway文件夹

Milkyway是Synopsys用于保存版图所有信息的格式,创建自己的Milkyway文件夹用来保存ICC过程中的文件。

读入门级网表,所有的模块都集中在角落,需要加入后续的布局布线信息。![图片[2] - Synopsys ICC简单教程 - 我的学记|刘航宇的博客 图片[2] - Synopsys ICC简单教程 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63d0e50d588a5d166c57d5e3.jpg)

3、布局规划floorplan

布局主要包含芯片大小的规划、IO单元的规划、宏单元的规划、电源网络的设计等。

读入.def文件,包含了整体的布局信息,这个文件需要另外经过许多操作产生:![图片[3] - Synopsys ICC简单教程 - 我的学记|刘航宇的博客 图片[3] - Synopsys ICC简单教程 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63d0e5c6588a5d166c58f316.jpg)

floorplan一旦确定,整个芯片的面积就定下来了,并且和整个设计的timing、布通率密切相关。

4、布局placement

placement是将一个个标准单元模块放入中间区域,通过place_opt自动排布![图片[4] - Synopsys ICC简单教程 - 我的学记|刘航宇的博客 图片[4] - Synopsys ICC简单教程 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63d0e63c588a5d166c59b498.jpg)

5、时钟树综合CTS

时钟树综合的主要目的是减小内部各个时钟的偏斜。时钟源必须通过一级一级的buffer才能驱动众多内部时钟,buffer采用上下延时对称的反相器。

下图是时钟树综合后的布局,内部的标准单元会重新排布:![图片[5] - Synopsys ICC简单教程 - 我的学记|刘航宇的博客 图片[5] - Synopsys ICC简单教程 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63d0e7a3588a5d166c5be467.jpg)

下图高亮了时钟树的内部走线![图片[6] - Synopsys ICC简单教程 - 我的学记|刘航宇的博客 图片[6] - Synopsys ICC简单教程 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63d0e7d4588a5d166c5c3897.jpg)

6、布线routing

布线会经过全局布线(Global routing 和详细布线 (Detail Routing)两个步骤,通过route_opt完成:![图片[7] - Synopsys ICC简单教程 - 我的学记|刘航宇的博客 图片[7] - Synopsys ICC简单教程 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63d0e80f588a5d166c5c91b9.jpg)

三、ICC注释详解

############################################################

# 1、逻辑库、技术库等基本参数设定

############################################################

lappend search_path ../ref/db ../ref/tlup

set_app_var target_library "sc_max.db"

set_app_var link_library "* sc_max.db io_max.db ram16x128_max.db"

set_min_library sc_max.db -min_version sc_min.db

set_min_library io_max.db -min_version io_min.db

set_min_library ram16x128_max.db -min_version ram16x128_min.db

# - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

# RISC_CHIP setup variables

# - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

set my_mw_lib risc_chip.mw

set mw_path "../ref/mw_lib"

set tech_file " ../ref/tech/cb13_6m.tf"

set tlup_map "../ref/tlup/cb13_6m.map"

set tlup_max "../ref/tlup/cb13_6m_max.tluplus"

set tlup_min "../ref/tlup/cb13_6m_min.tluplus"

set top_design "RISC_CHIP"

set verilog_file "./design_data/RISC_CHIP.v"

set sdc_file "./design_data/RISC_CHIP.sdc"

set def_file "./design_data/RISC_CHIP.def"

set ctrl_file "./scripts/opt_ctrl.tcl"

set derive_pg_file "./scripts/derive_pg.tcl"

set MODULE_NAME RISC_CHIP

############################################################

# 2、创建自己的Milkyway文件夹

############################################################

file delete -force $my_mw_lib

create_mw_lib $my_mw_lib -open -technology $tech_file \

-mw_reference_library "$mw_path/sc $mw_path/io $mw_path/ram16x128"

#加载门级网表文件

import_designs $verilog_file \

-format verilog \

-top $top_design

#加载线负载模型

set_tlu_plus_files \

-max_tluplus $tlup_max \

-min_tluplus $tlup_min \

-tech2itf_map $tlup_map

#加载VDD、VSS信息

source $derive_pg_file

#加载约束文件

read_sdc $sdc_file

source $ctrl_file

source scripts/zic_timing.tcl

exec cat zic.timing

remove_ideal_network [get_ports scan_en]

save_mw_cel -as RISC_CHIP_data_setup

############################################################

# 3、布局规划floorplan

############################################################

# 读入布局信息并布局

read_def $def_file

set_pnet_options -complete {METAL3 METAL4}

save_mw_cel -as RISC_CHIP_floorplanned

############################################################

# 4、布局placement,放置基本单元

############################################################

place_opt

redirect -tee place_opt.timing {report_timing}

report_congestion -grc_based -by_layer -routing_stage global

save_mw_cel -as RISC_CHIP_placed

############################################################

# 5、时钟树综合clock tree synthesis

############################################################

remove_clock_uncertainty [all_clocks]

set_fix_hold [all_clocks]

#时钟树综合

clock_opt

redirect -tee clock_opt.timing {report_timing}

# 保存文件

save_mw_cel -as RISC_CHIP_cts

############################################################

# 6、布线routing

############################################################

route_opt

#报告物理信息

report_design -physical

save_mw_cel -as RISC_CHIP_routed

############################################################

# 7、输出文件

############################################################

file mkdir icc_files

write -format ddc -hierarchy -output icc_files/$MODULE_NAME.apr.ddc

write_verilog -no_tap_cells icc_files/$MODULE_NAME.lvs.v -pg -no_core_filler_cells

write_verilog -no_tap_cells icc_files/$MODULE_NAME.sim.v -no_core_filler_cellssynopsys的实验礼包