在ASIC/FGPA设计中,我们外界控制所设计的模块时候需要实现告诉他,我要给你输入信号了,你的工作了,反之你不用工作,这个就是门控时钟,就是使能信号EN,一般来说我们用EN控制CLK的产生。芯片功耗组成中,有高达40%甚至更多是由时钟树消耗掉的。这个结果的原因也很直观,因为这些时钟树在系统中具有最高的切换频率,而且有很多时钟buffer,而且为了最小化时钟延时,它们通常具有很高的驱动强度。此外,即使输入和输出保持不变,接收时钟的触发器也会消耗一定的功耗。而且这些功耗主要是动态功耗。

那么减少时钟网络的功耗消耗,最直接的办法就是如果不需要时钟的时候,就把时钟关掉。这种方法就是大家熟悉的门控时钟:clock gating。(大家电路图中看到的CG cell就是门控时钟了)

1门控时钟的结构

1.1与门门控

如果让我们设计一个门控时钟的电路,我们会怎么设计呢?最直接的方法,不需要时钟的时候关掉时钟,这就是与操作,我们只需要把enable和CLK进行“与”操作不就行了么,电路图如下:![图片[1] - Verilog RTL级低功耗设计-门控时钟及时钟树 - 我的学记|刘航宇的博客 图片[1] - Verilog RTL级低功耗设计-门控时钟及时钟树 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63c56342be43e0d30e67741c.jpg)

这种直接将控制EN信号和时钟CLK进行与操作完成门控的方式,可以完成EN为0时,时钟被关掉。但是同时带来另外一个很大的问题:毛刺![图片[2] - Verilog RTL级低功耗设计-门控时钟及时钟树 - 我的学记|刘航宇的博客 图片[2] - Verilog RTL级低功耗设计-门控时钟及时钟树 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63c563c1be43e0d30e682b9a.jpg)

如上图所示,EN是不受控制的,随时可能跳变,这样纯组合输出GCLK就完全可能会有毛刺产生。时钟信号上产生毛刺是很危险的。实际中,这种直接与门的方式基本不会被采样。

所以我们需要改进电路,为了使门控时钟不产生毛刺,我们必须对EN信号进行处理,使其在CLK的高低电平期间保持不变,或者说EN的变化就是以CLK为基准的。

1 很自然的我们会想到触发器,只要把EN用CLK寄存一下,那么输出就是以CLK为基准的;

2 其实还有一种办法是锁存器,把EN用锁存器锁存的输出,也是以CLK为基准的。

1.2 锁存门控

我们先看一下第二种电路,增加锁存器的电路如下:![图片[3] - Verilog RTL级低功耗设计-门控时钟及时钟树 - 我的学记|刘航宇的博客 图片[3] - Verilog RTL级低功耗设计-门控时钟及时钟树 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63c565e3be43e0d30e6bef6e.jpg)

对应的时序如下:![图片[4] - Verilog RTL级低功耗设计-门控时钟及时钟树 - 我的学记|刘航宇的博客 图片[4] - Verilog RTL级低功耗设计-门控时钟及时钟树 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63c56661be43e0d30e6cb09a.jpg)

可以看到,只有在CLK为高的时候,GCLK才可能会输出高,这样就能消除EN带来的毛刺。这是因为D锁存器是电平触发,在clk=1时,数据通过D锁存器流到了Q;在Clk=0时,Q保持原来的值不变。

虽然达到了我们消除毛刺的目的,但是这个电路还有两个缺点:

1如果在电路中,锁存器与与门相隔很远,到达锁存器的时钟与到达与门的时钟有较大的延迟差别,则仍会出现毛刺。

2 如果在电路中,时钟使能信号距离锁存器很近,可能会不满足锁存器的建立时间,会造成锁存器输出出现亚稳态。

如下图分析所示:![图片[5] - Verilog RTL级低功耗设计-门控时钟及时钟树 - 我的学记|刘航宇的博客 图片[5] - Verilog RTL级低功耗设计-门控时钟及时钟树 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63c567b9be43e0d30e6f8d3c.jpg)

上述的右上图中,B点的时钟比A时钟迟到,并且Skew > delay,这种情况下,产生了毛刺。为了消除毛刺,要控制Clock Skew,使它满足Skew

1.3 寄存门控

如1.1中提到的,我们还有另外的解决办法,就是用寄存器来寄存EN信号再与上CLK得到GCLK,电路图如下所示:![图片[6] - Verilog RTL级低功耗设计-门控时钟及时钟树 - 我的学记|刘航宇的博客 图片[6] - Verilog RTL级低功耗设计-门控时钟及时钟树 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63c568e4be43e0d30e729449.jpg)

时序如下所示:![图片[7] - Verilog RTL级低功耗设计-门控时钟及时钟树 - 我的学记|刘航宇的博客 图片[7] - Verilog RTL级低功耗设计-门控时钟及时钟树 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63c5690bbe43e0d30e7315af.jpg)

由于DFF输出会delay一个周期,所以除非CLKB上升沿提前CLKA很多,快半个周期,才会出现毛刺,而这种情况一般很难发生。但是,这种情况CLKB比CLKA迟到,是不会出现毛刺的。

当然,如果第一个D触发器不能满足setup时间,还是有可能产生亚稳态。

1.4 门控时钟结构选择

那么到底采用哪一种门控时钟的结构呢?是锁存结构还是寄存结构呢?通过分析,我们大概会选择寄存器结构的门控时钟,这种结构比锁存器结构的问题要少,只需要满足寄存器的建立时间就不会出现问题。

那么实际中是这样么?答案恰恰相反,SOC芯片设计中使用最多的却是锁存结构的门控时钟。

原因是:在实际的SOC芯片中,要使用大量的门控时钟单元。所以通常会把门控时钟做出一个标准单元,有工艺厂商提供。那么锁存器结构中线延时带来的问题就不存在了,因为是做成一个单元,线延时是可控和不变的。而且也可以通过挑选锁存器和增加延时,总是能满足锁存器的建立时间,这样通过工艺厂预先把门控时钟做出标准单元,这些问题都解决了。

那么用寄存器结构也可以达到这种效果,为什么不用寄存器结构呢?那是因为面积!一个DFF是由两个D锁存器组成的,采样D锁存器组成门控时钟单元,可以节省一个锁存器的面积。当大量的门控时钟插入到SOC芯片中时,这个节省的面积就相当可观了。

所以,我们在工艺库中看到的标准门控时钟单元就是锁存结构了:![图片[8] - Verilog RTL级低功耗设计-门控时钟及时钟树 - 我的学记|刘航宇的博客 图片[8] - Verilog RTL级低功耗设计-门控时钟及时钟树 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63c56a1cbe43e0d30e752a70.jpg)

当然,这里说的是SOC芯片中使用的标准库单元。如果是FPGA或者用RTL实现,个人认为还是用寄存器门控加上setup约束来实现比较稳妥。

门控时钟代码

always@(CLK or CLK_EN)

if(!CLK)

CLK_TEMP<=CLK_EN

assign GCLK=CLK&CLK_TEMP2 RTL中的门控时钟

通常情况下,时钟树由大量的缓冲器和反相器组成,时钟信号为设计中翻转率最高的信号,时钟树的功耗可能高达整个设计功耗40%。

加入门控时钟电路后,由于减少了时钟树的翻转,节省了翻转功耗。同时,由于减少了寄存器时钟引脚的翻转行为,寄存器的内部功耗也减少了。采用门控时钟,可以非常有效地降低设计的功耗,一般情况下能够节省20%~60%的功耗。

那么RTL中怎么才能实现门控时钟呢?答案是不用实现。现在的综合工具比如DC会自动插入门控时钟。如下图所示:![图片[9] - Verilog RTL级低功耗设计-门控时钟及时钟树 - 我的学记|刘航宇的博客 图片[9] - Verilog RTL级低功耗设计-门控时钟及时钟树 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63c56aadbe43e0d30e75f1ba.jpg)

这里有两点需要注意:

- 插入门控时钟单元后,上面电路中的MUX就不需要了,如果数据D是多bit的(一般都是如此),插入CG后的面积可能反而会减少;

- 如果D是单bit信号,节省的功耗就比较少,但是如果D是一个32bit的信号,那么插入CG后节省的功耗就比较多了。

这里的决定因素就是D的位宽了,如果D的位宽很小,那么可能插入的CG面积比原来的MUX大很多,而且节省的功耗又很少,这样得不偿失。只有D位宽超过了一定的bit数后,插入CG的收益就比较大。

那么这个临界值是多少呢?不同的工艺可能不一样,但是DC给的默认值是3.

也就是说,如果D的位宽超过了3bit,那么DC就会默认插入CG,这样综合考虑就会有收益。

我们可以通过DC命令:

set_clock_gating_style -minimum_bitwidth 4

来控制芯片中,对不同位宽的寄存器是否自动插入CG。一般情况都不会去修改它。

附加:门控时钟的时钟树设计

在时钟树的设计中,门控时钟单元应尽量摆放在时钟源附近,即防止在门控时钟单元的前面摆放大量的时钟缓冲器(Buffer)。 这样,在利用门控时钟电路停时钟时不仅能将该模块中的时钟停掉,也能将时钟树上的时钟缓冲器停止反转,有效地控制了时钟树上的功耗。如图11-24所示,在布局时将门控时钟电路的部件摆放在一起,并摆放在时钟源GCLK附近,停掉时钟后,整个时钟树_上的缓冲器(CTS)和时钟树驱动的模块都停止了翻转。通常的SoC设计中,门控时钟单元会被做成一个硬核或标准单元。![图片[10] - Verilog RTL级低功耗设计-门控时钟及时钟树 - 我的学记|刘航宇的博客 图片[10] - Verilog RTL级低功耗设计-门控时钟及时钟树 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/6417d54aa682492fcc3d1513.jpg)

3 RTL 门控时钟编码风格

组合逻辑中,为避免生成锁存器,好的代码风格是if语句都加上else,case语句都加上default。

时序逻辑中,为了让综合工具能够自动生成门控时钟,好的代码风格则是“若无必要,尽量不加else和default”——以减小数据翻转机会。

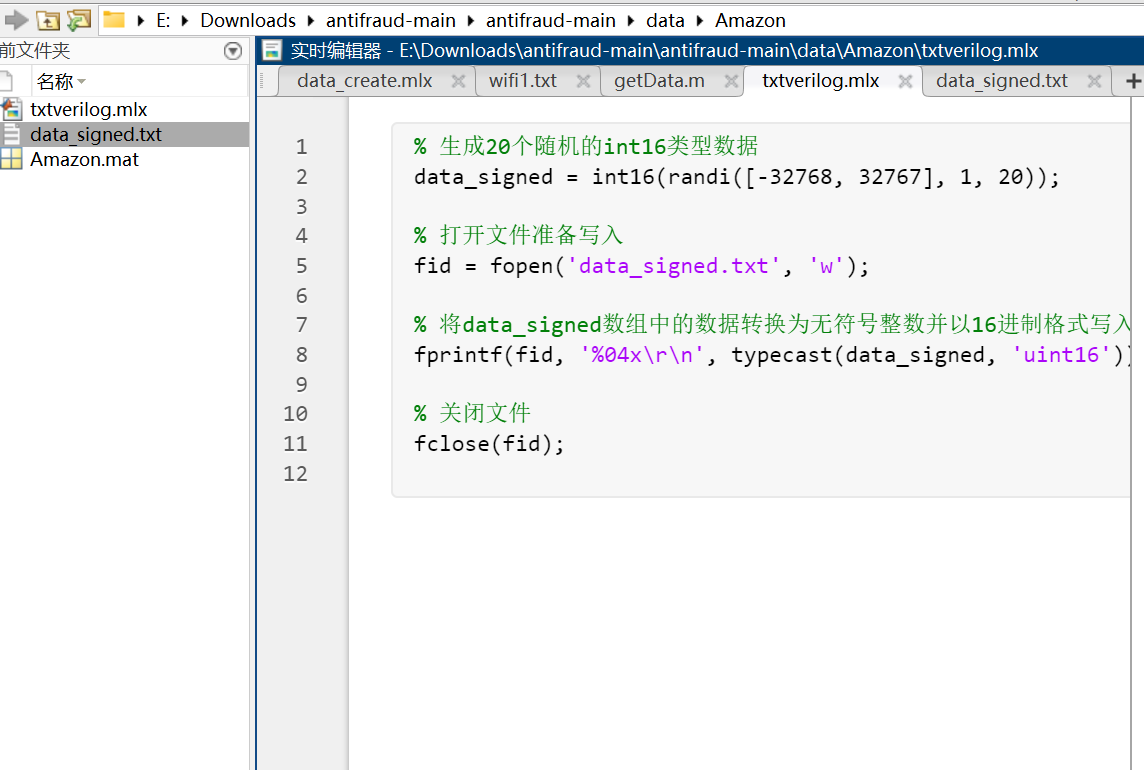

虽然现在综合工具可以自动插入门控时钟,但是如果编码风格不好,也不能达到自动插入CG的目的。比较下面两种RTL写法:![图片[11] - Verilog RTL级低功耗设计-门控时钟及时钟树 - 我的学记|刘航宇的博客 图片[11] - Verilog RTL级低功耗设计-门控时钟及时钟树 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63c56bcebe43e0d30e780e73.jpg)

左边的RTL代码能够成功的综合成自动插入CG的电路;

右边的RTL不能综合成插入CG的电路;

右边电路在d_valid为低时,d_out也会一直变化,其实没有真正的数据有效的指示信号,所以综合不出来插入CG的电路。

需要注意的是,有的前端设计人员,为了仿真的时候看的比较清楚,很容易会写成右边的代码,这样不仅不能在综合的时候自动插入CG来减少功耗;而且增加了d_out的翻转率,进一步增加了功耗。

在不用的时候把数据设成0并不能减少功耗,保持数据不变化才能减少toggle,降低功耗!

所以我们在RTL编写的时候一定要注意。

作为前端设计者,了解这些知识就足够了,如果想深入了解综合的控制,可以去了解

set_clock_gating_style 这个核心控制命令

后记

门控时钟是低功耗技术的一种常规方法,应用已经很成熟了,所以很多人会忽视它的存在和注意事项,也不了解它的具体时序。本文从SOC前端设计的角度详细解释了各种门控时钟的结构和RTL编码需要注意的事项,希望能对设计人员有所帮助。