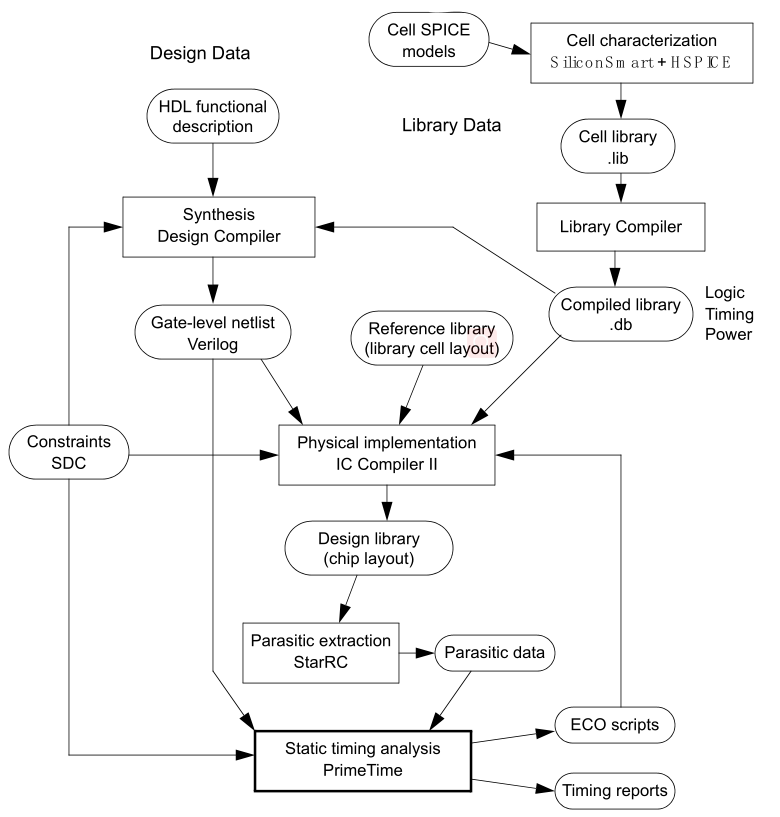

参考书:数字集成电路-电路、系统与设计,本文栏目对其重点进行精简化

传输管逻辑

1. 有比逻辑

传输管逻辑是有比逻辑;互补CMOS是无比逻辑。

简单而言,

无比逻辑:输出的高低电平和尺寸无关。比如互补CMOS可以直接把输出电压拉到VDD或者GND

有比逻辑:输出的高低电平和尺寸有关。基本没办法直接拉到最大逻辑摆幅。

上拉网络由一个负载代替,如下三种常见的负载(电阻负载、有源负载、伪NMOS负载)![图片[1] - VLSI设计基础7-传输管与传输门逻辑 - 我的学记|刘航宇的博客 图片[1] - VLSI设计基础7-传输管与传输门逻辑 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f77c75f144a01007e9935b.jpg)

![图片[2] - VLSI设计基础7-传输管与传输门逻辑 - 我的学记|刘航宇的博客 图片[2] - VLSI设计基础7-传输管与传输门逻辑 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f7809cf144a01007f0e990.jpg)

![图片[3] - VLSI设计基础7-传输管与传输门逻辑 - 我的学记|刘航宇的博客 图片[3] - VLSI设计基础7-传输管与传输门逻辑 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f780cff144a01007f14615.jpg)

输出端的电压摆幅和门的功能取决于NMOS和PMOS的尺寸比

对于伪NMOS管负载

优点:逻辑门减小,面积减小,只需要n+1个管子,而互补CMOS需要2n个管子

缺点:

有比逻辑,达不到最大逻辑摆幅。

可能没办法完全关断MOS管,静态功耗增加。

应用:面积要求严格,性能要求不高的场景。

2. 传输管逻辑

- 区别

传输管逻辑和互补CMOS有以下差别:![图片[4] - VLSI设计基础7-传输管与传输门逻辑 - 我的学记|刘航宇的博客 图片[4] - VLSI设计基础7-传输管与传输门逻辑 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f77d7ff144a01007eb4423.jpg)

串联

综合以上的区别,原因主要出在于输入端可以从D、G,而输出从S,从而使输出和输入之间存在VTH的压降

为了减小VTH带来的影响,传输管串联采用D-S-D-S的方式,而不采用D-S-G-S的方式

前者只有一个VTH压降,而后者有两个

如下:![图片[5] - VLSI设计基础7-传输管与传输门逻辑 - 我的学记|刘航宇的博客 图片[5] - VLSI设计基础7-传输管与传输门逻辑 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f77e01f144a01007ec2549.jpg)

3. 互补传输管逻辑(CPL)

优点:

互补输入输出

每个输出节点都有一个低阻路径连接到VDD或者GND

模块化

缺点:

存在VTH,充电充不到VDD,只能充到VDD-VTH

解决方法:电平恢复、多种阈值晶体管、传输门逻辑

确定输出:![图片[6] - VLSI设计基础7-传输管与传输门逻辑 - 我的学记|刘航宇的博客 图片[6] - VLSI设计基础7-传输管与传输门逻辑 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f77ee3f144a01007ed9fc5.jpg)

![图片[7] - VLSI设计基础7-传输管与传输门逻辑 - 我的学记|刘航宇的博客 图片[7] - VLSI设计基础7-传输管与传输门逻辑 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f77ef9f144a01007edc53d.jpg)

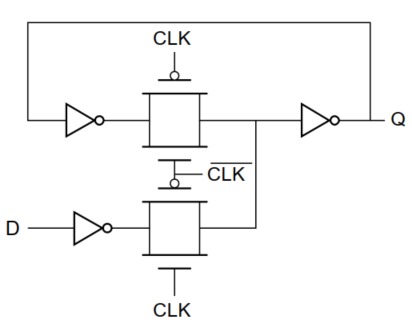

3. 传输门逻辑

![图片[8] - VLSI设计基础7-传输管与传输门逻辑 - 我的学记|刘航宇的博客 图片[8] - VLSI设计基础7-传输管与传输门逻辑 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f7816af144a01007f259f2.jpg)

有比逻辑分类和串联部分的图片放反了