参考书:数字集成电路-电路、系统与设计,本文栏目对其重点进行精简化

1. 总论

在时序电路中,时序电路=组合电路+存储电路

在(9)~(11)中,已经详细介绍了存储电路(寄存器)

在本文中,将介绍组合电路中比较重要的数据通路上的电路,可以认为是在时序电路中提到的

,即用于逻辑运算和算数运算。

在数集中,常用的数据通路组合电路有

加法器

乘法器

移位器

我们的目的,是追求以下几个方面的优化

性能

面积

功耗

如何优化:

逻辑层次优化:利用状态机、真值表等,优化布尔方程得到一个速度更快、面积更小的电路

电路层次优化:改变管子的尺寸;改变电路的拓扑连接(互补CMOS、动态CMOS等)

2. 加法器

加法器在数据通路电路中的地位类似于反相器在与或等简单逻辑电路的位置

数据通路的电路的基础是加法器

乘法器也是加法器扩展而来的

加法器是限制数据通路运算速度的元件。

1. 一位全加器(FA)

- 传统表达方式

定义:根据输入的二值数据、进位信号,计算得到结果和进位。![图片[1] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[1] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f83714f144a01007d6022f.jpg)

![图片[2] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[2] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63fc2046f144a010075b848a.jpg)

【注】:

异或,常见结构有:![图片[3] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[3] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63fc2065f144a010075badb4.jpg)

同或,结构如下(即“异或门结构2”的“非”):![图片[4] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[4] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63fc2091f144a010075be379.jpg)

- P、G、D函数表达

真值表如下:![图片[5] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[5] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63fc20fff144a010075c65cb.jpg)

![图片[6] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[6] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63fc2113f144a010075c7e5a.jpg)

逐位(行波)加法器

所谓逐位(行波)加法器,指的是将N个一位全加器(FN)串联在一起构成加法器。如下图![图片[7] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[7] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63fc2144f144a010075cb9ee.jpg)

![图片[8] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[8] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63fc2159f144a010075cd6d3.jpg)

2. 【结构】设计全加器FA

- 互补静态CMOS结构FA

![图片[9] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[9] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63fc21cbf144a010075d65f3.jpg)

![图片[10] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[10] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63fc21f6f144a010075da102.jpg)

镜像加法器

该加法器是根据互补静态CMOS结构FA改进得到的,镜像加法器的下拉网络和互补CMOS结构FA完全相同。

电路图如图所示,![图片[11] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[11] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63fc222af144a010075de1b2.jpg)

![图片[12] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[12] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63fc2258f144a010075e1769.jpg)

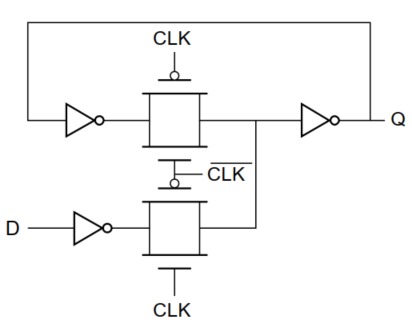

3. 传输门型加法器——传统型

![图片[13] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[13] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f870b8f144a010073096e7.jpg)

![图片[14] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[14] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63fc22faf144a010075ee79d.jpg)

4. 传输门型加法器——曼切斯特FA

- 静态电路

![图片[15] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[15] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f8727bf144a01007332d74.jpg)

![图片[16] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[16] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63fc252ef144a0100762bcb3.jpg)

- 动态电路

![图片[17] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[17] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f872dbf144a0100733b2ef.jpg)

动态电路简单

动态电路单向工作,传输门使用NMOS管实现

该电路不需要D - 曼切斯特进位链加法器

![图片[18] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[18] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f872f7f144a0100733d4ad.jpg)

![图片[19] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[19] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63fc276ef144a01007670937.jpg)

- 【逻辑】设计全加器FA

- 旁路进位加法器

![图片[20] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[20] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f87323f144a010073410b4.jpg)

![图片[21] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[21] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63fc279ef144a010076747ba.jpg)

延时![图片[22] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[22] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f87358f144a01007345bcc.jpg)

$t_{\text {adder }}=t_{\text {setup }}+M t_{\text {carry }}+\left(\frac{N}{M}-1\right) t_{\text {bypass }}+(M-1) t_{\text {carry }}+t_{\text {sum }}$ - 线性进位选择加法器

![图片[23] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[23] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63fc281bf144a0100767dd20.jpg)

![图片[24] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[24] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63fc284bf144a01007681258.jpg)

![图片[25] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[25] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63fc2862f144a01007682d85.png)

![图片[26] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[26] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63fc2888f144a010076853c1.jpg)

平方根进位加法器

![图片[27] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[27] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f8740af144a010073546c5.jpg)

![图片[28] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[28] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63fc28c4f144a01007689ab4.jpg)

![图片[29] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[29] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63fc28d4f144a0100768ac81.jpg)

4. 【重要】超前进位加法器

- 原理

![图片[30] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[30] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f874a9f144a01007363ba1.jpg)

![图片[31] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[31] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63fc290ff144a0100768f416.jpg)

![图片[32] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[32] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f874e4f144a01007368f7e.jpg)

![图片[33] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[33] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f874eef144a01007369e5a.jpg)

- 块运算

![图片[34] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[34] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63fc2964f144a01007695fbb.jpg)

![图片[35] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[35] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f87535f144a0100737069e.jpg)

![图片[36] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[36] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63fc298df144a01007699387.jpg)

- 点操作

步骤如下:![图片[37] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[37] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63fc29c8f144a0100769d60d.jpg)

![图片[38] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[38] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63fc29eff144a0100769fe82.jpg)

![图片[39] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[39] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63fc2a13f144a010076a2423.jpg)

- Kogge-Stone 16位超前进位加法器

![图片[40] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[40] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63fc2a2ef144a010076a4911.jpg)

![图片[41] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[41] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63fc2a40f144a010076a5fb4.jpg)

- Brent-Kung 16位超前进位加法器

![图片[42] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[42] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f87621f144a0100739082c.jpg)

![图片[43] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客 图片[43] - VLSI设计基础11-运算模块之加法器 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63fc2a67f144a010076a8c78.jpg)