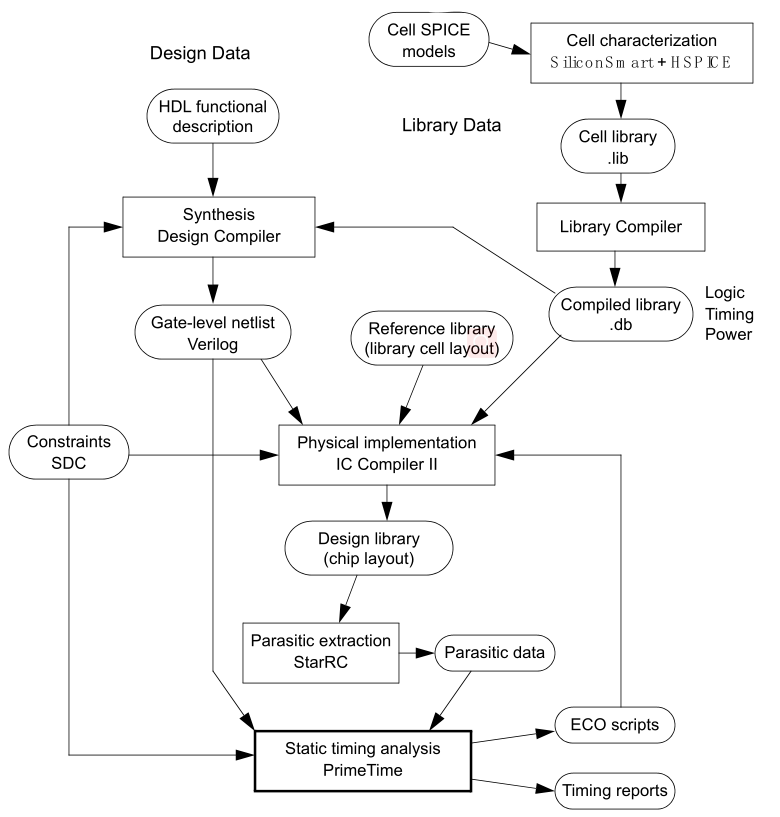

参考书:数字集成电路-电路、系统与设计,本文栏目对其重点进行精简化

静态CMOS:稳态时,通过低阻路径连接VDD或GND

互补CMOS:上下网络互补,上拉到VDD,下拉到GND。管子数为2N

传输管逻辑:上拉网络用其他代替,有比逻辑,存在VTH。管子数为N+1

动态CMOS:依靠高阻抗上的电容存储临时的信号。管子数为N+2![图片[1] - VLSI设计基础8-动态COMS - 我的学记|刘航宇的博客 图片[1] - VLSI设计基础8-动态COMS - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f78540f144a01007f90205.jpg)

1. 综述

结构如下,![图片[2] - VLSI设计基础8-动态COMS - 我的学记|刘航宇的博客 图片[2] - VLSI设计基础8-动态COMS - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f78359f144a01007f5c418.jpg)

工作方式:工作分为两个阶段

预充电:CLK=0,Mp导通,对CL充电

求值:CLK=1,MN导通,OUT和GND之间存在低阻通路。

特点:

全电压摆幅

无比逻辑(同互补CMOS,异传输管逻辑)

噪声容限低。因为out在预充电阶段已经充电到VDD,即VDS已经满足>VOV,于是只要VIN>VTH,管子就会导通。

需要预充电和求值的时钟。

较快的开关速度。原因如下,

相对互补CMOS,缺少了上拉网络的一个门,相对负载是互补CMOS,负载是动态门的CL比较小

动态门没有短路电流(同一个时刻,只能一个导通),由下拉网络提供的所有电流都用于CL电容的放电

如果IN=0,则不存在输出延时(预充电完输出即为1);如果IN=1,则需要CL放电

晶体管重复利用,减小面积(多输出多米诺)

优点:

提高速度

减小面积(多输出多米诺;N+2个管子)

没有短路功耗

没有毛刺(因为一次只能翻转一次,CL放电完只能等效下一次预充电才能回到1)

2. 存在的问题——信号完整性问题

电荷泄露

来源:与CL相连的管子存在反偏二极管和亚阈值漏电。![图片[3] - VLSI设计基础8-动态COMS - 我的学记|刘航宇的博客 图片[3] - VLSI设计基础8-动态COMS - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f784f3f144a01007f87bf9.jpg)

解决办法:使用泄露晶体管

反馈形式的伪NMOS型上拉器件。

该晶体管为了减小功耗和尺寸,一般选用尺寸较小(电阻值大)的管子。![图片[4] - VLSI设计基础8-动态COMS - 我的学记|刘航宇的博客 图片[4] - VLSI设计基础8-动态COMS - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f78540f144a01007f90205.jpg)

电荷分享

来源:下拉网络中存在的节点电容CA。当A=0-》1、B=0,则原本存储在电容CL上的电荷在CL和CA之间重新分配,造成输出电压有所下降![图片[5] - VLSI设计基础8-动态COMS - 我的学记|刘航宇的博客 图片[5] - VLSI设计基础8-动态COMS - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f785f6f144a01007fa277e.jpg)

※需要满足A=0-》1、B=0才能进行电荷分享,否则当B=1的时候,求值过程中(CLK=1),CL存储的电荷将全部被释放掉,不存在点电荷分享现象![图片[6] - VLSI设计基础8-动态COMS - 我的学记|刘航宇的博客 图片[6] - VLSI设计基础8-动态COMS - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f787b9f144a01007fe6230.jpg)

3. 多米诺逻辑

多米诺逻辑即为前文所述的串联动态门,目的就是保证预充电时,输入均为0;求值时,输入只做0→1的翻转

$$ \text { 多米诺逻辑 }=n \text { 型动态门 }+\text { 反相器 } $$

![图片[7] - VLSI设计基础8-动态COMS - 我的学记|刘航宇的博客 图片[7] - VLSI设计基础8-动态COMS - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f7887df144a01007010e81.jpg)

初始状态均为0,求值的时候根据前一级输出确定下一级输入,从而求下一级输出。

特点:

求值层层传播,如多米诺骨牌

求值阶段的时间取决于逻辑深度(因为求值时候的特性,见上)

只能实现非反向逻辑

无比逻辑

节点需要在预充电充完电,求值的过程中,输入需要特别稳定。

速度非常快(因为当上一级的输入都是0时,下一级相当于无延迟传播)

输入电容小(和互补CMOS比,只有一个管子)

4. 组合多米诺逻辑

组合多米诺逻辑,并不需要在每个动态门之后加反相器,而是借助一个复合互补CMOS门将多个动态门组合起来。![图片[8] - VLSI设计基础8-动态COMS - 我的学记|刘航宇的博客 图片[8] - VLSI设计基础8-动态COMS - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f789a4f144a010070312ad.jpg)

eg:![图片[9] - VLSI设计基础8-动态COMS - 我的学记|刘航宇的博客 图片[9] - VLSI设计基础8-动态COMS - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f789b9f144a010070333fd.jpg)

![图片[10] - VLSI设计基础8-动态COMS - 我的学记|刘航宇的博客 图片[10] - VLSI设计基础8-动态COMS - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f789cbf144a01007034f10.jpg)