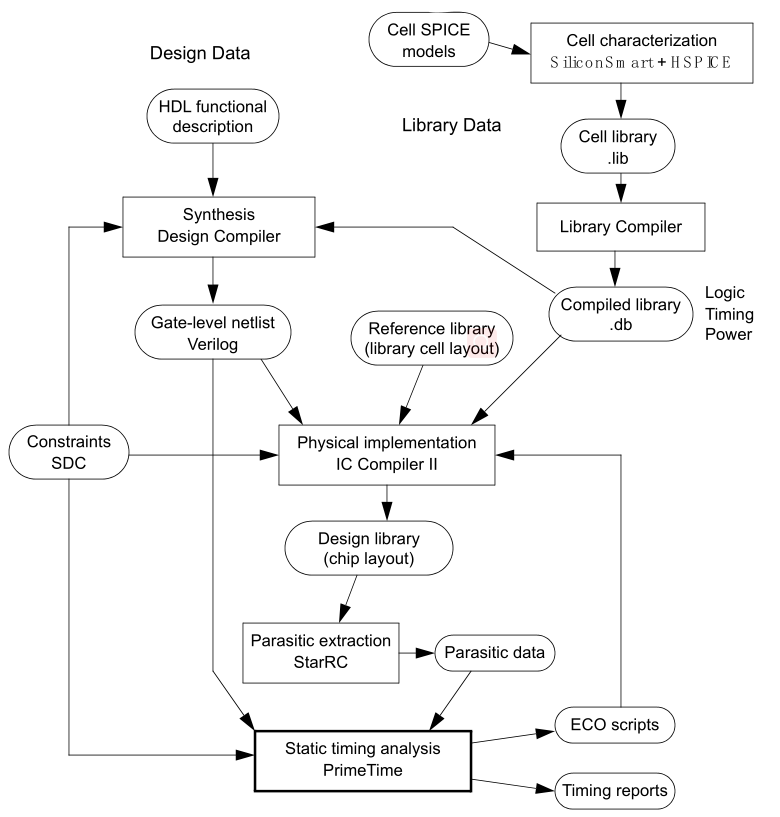

参考书:数字集成电路-电路、系统与设计,本文栏目对其重点进行精简化

1. 时序基础概念

- 时序分析的目的

对数字系统进行时序检查,判断电路是否可以正常工作(常面临建立时间和保持时间等问题),判断电路的性能等。

常常分析电压、温度、工艺(工艺角)等参数进行分析。

2. 时序分析的分类

- 静态时序分析(STA)

主要研究对象:建立时间、保持时间、传播延时

常用于分析同步时序电路(源时钟和目的时钟相同)

时序分析模型:

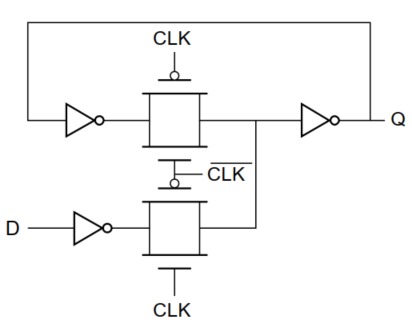

同步时钟/异步时钟

D触发器分割组合逻辑![图片[1] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客 图片[1] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f813eff144a01007a2127c.jpg)

一般不需要进行太复杂的仿真,仅需要计算就可以进行分析,运行速度快。

不依赖于激励,根据穷尽信号路径上的器件就可以进行计算

常用方法是使用查找表——①输入跳变时间②输出负载(电容)→①传播延时②输出跳变(下一级的输入跳变)。

- 动态时序分析(DTA)

指门级仿真

主要用于异步逻辑、多周期路径

在FPGA中,将RTL代码综合利用综合工具综合成门级网络进行仿真,其中各种门级器件的逻辑是厂家提供的。 - 【时钟】沿

发送沿:发送数据的源时钟活动沿

捕获沿:接收数据的目的时钟的活动沿

源时钟:用于发送数据的时钟

目的时钟:用于接受数据的时钟

小贴士:在同步电路中,源时钟和目的时钟是同一个

4. 时序约束参数(重点)

即:建立时间tsu、保持时间thold、传播延时tc-q,同时我们引入污染时间tcd

- 建立时间:

对于捕获沿到来之前,数据需要保持稳定的时间

间接约束了组合逻辑的最大延时 - 保持时间:

对于捕获沿到来之后,数据需要保持稳定的时间

间接约束了组合逻辑的最小延时 - 传播时间(延时):

即 最大延时 时间

捕获沿50%(数据输入沿50%【注意:数据输入沿其实就是捕获沿!!!】)到数据稳定输出(输出数据50%)的时间

根据器件不同,可以分为组合逻辑传播延时tlogic和寄存器传播延时tc-q,详细见后文。

- 污染时间:

可以理解为 最短延时 时间——理想状态下

从输入“扰动”到输出“扰动”的时间,下文进行解释。

根据器件不同,可以分为组合逻辑污染延时tlogic,cd和寄存器污染延时tc-q,cd,详细见后文

所谓理想状态,指的是数据没有跳变时间,即数据跳变是瞬间完成的,数据跳变的90%、50%、10%是在同一个时间。

根据以上理想状态的定义,可认为一有扰动,数据就跳变完成。 计算污染时间和传播时间

![图片[2] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客 图片[2] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f81762f144a01007a8fb96.jpg)

现对图中四个时间进行解释:![图片[3] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客 图片[3] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f82c9cf144a01007c58c68.jpg)

![图片[4] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客 图片[4] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f82cb2f144a01007c5a71d.jpg)

5. 各种信号路径、时序路径

信号的路径主要分为三个

![图片[5] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客 图片[5] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f82d0cf144a01007c61ebd.jpg)

时钟路径

源时钟路径&目的时钟路径![图片[6] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客 图片[6] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f82d4df144a01007c67544.jpg)

数据路径![图片[7] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客 图片[7] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f82d9cf144a01007c6db71.jpg)

数据起点:

对于时序逻辑电路,为某时序单元的时钟引脚

对于组合逻辑电路,为某逻辑单元的数据输入端口

数据终点:

对于组合逻辑电路、时序逻辑电路都一样,均为某单元的数据输出端口

异步路径(如异步复位)

根据路径可将分析类型分为

同步分析:时钟路径+数据路径

异步分析:时钟路径+异步路径6. 时钟参数两大条件(重点)

- 周期条件

![图片[8] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客 图片[8] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f82de4f144a01007c73e2f.jpg)

保持时间条件

![图片[9] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客 图片[9] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f82e7ef144a01007c803a6.jpg)

![图片[10] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客 图片[10] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f82fc1f144a01007ca24af.jpg)

2. 时间偏差与抖动(重点)

理想时钟:

从时钟沿到各个单元的时钟端口的延时相等(即路径均匀);

同一个时刻,各个单元的时钟端的时钟相位相等。

实际时钟:

时钟偏差:各个时钟端口的时钟的周期没有改变,但是相位可能略有差别。

时钟抖动:时钟的周期存在一些差别,或长或短。1. 时钟偏差(Clock Skew)

- 定义与成因

指同一个时钟域之间,时钟信号到达各个寄存器的最大时间差

产生原因:

时钟源到达各个端点的路径长度不同

各个端口的负载不同

时钟网络中插入的缓存器不等 - 计算【全局偏差、局部偏差】

![图片[11] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客 图片[11] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f83069f144a01007cb92c6.jpg)

- 全局时钟偏差

![图片[12] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客 图片[12] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f830e6f144a01007ccfb89.jpg)

- 局部时钟偏差

![图片[13] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客 图片[13] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f83114f144a01007cd9677.jpg)

- 时钟偏差分类(正负)

- 正偏差

正偏差,即时钟延迟方向与数据流方向一致,如图所示。![图片[14] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客 图片[14] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f8316bf144a01007ce2df0.jpg)

- 负偏差

正偏差,即时钟延迟方向与数据流方向相反,如图所示。![图片[15] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客 图片[15] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f83202f144a01007cf109d.jpg)

- 利用时间偏差修补建立时间

![图片[16] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客 图片[16] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f8326bf144a01007cfa2ad.jpg)

【周期T】时钟偏差对于周期的影响

前文提到,负偏差使得实际逻辑计算的时间减小,为了填补裕量,只能增加时间周期,而提高时间周期会使得电路的性能下降。![图片[17] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客 图片[17] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f833e7f144a01007d19236.jpg)

2. 时钟抖动(Clock Jitter)

- 定义与计算

定义:芯片某一给定点上,时钟周期宽度发生变化,或缩短或变宽

计算:![图片[18] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客 图片[18] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f8349ef144a01007d2671c.jpg)

![图片[19] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客 图片[19] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f834b9f144a01007d28acf.jpg)

- 【周期T】时钟抖动对于周期的影响

因为时钟抖动是难以预料的,在确定时钟周期的时候,我们应该考虑最坏的情况,即$T-2 t_{\text {jitter }}>t_{c-q}+t_{\text {logic }}+t_{s u}$

即上图所示的③-④。因为这意味着周期T需要增加tjitter,性能降低 - 总结

![图片[20] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客 图片[20] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f83553f144a01007d34cd8.jpg)

![图片[21] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客 图片[21] - VLSI设计基础10-时序逻辑电路设计(二) - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f835b9f144a01007d3bc8c.jpg)