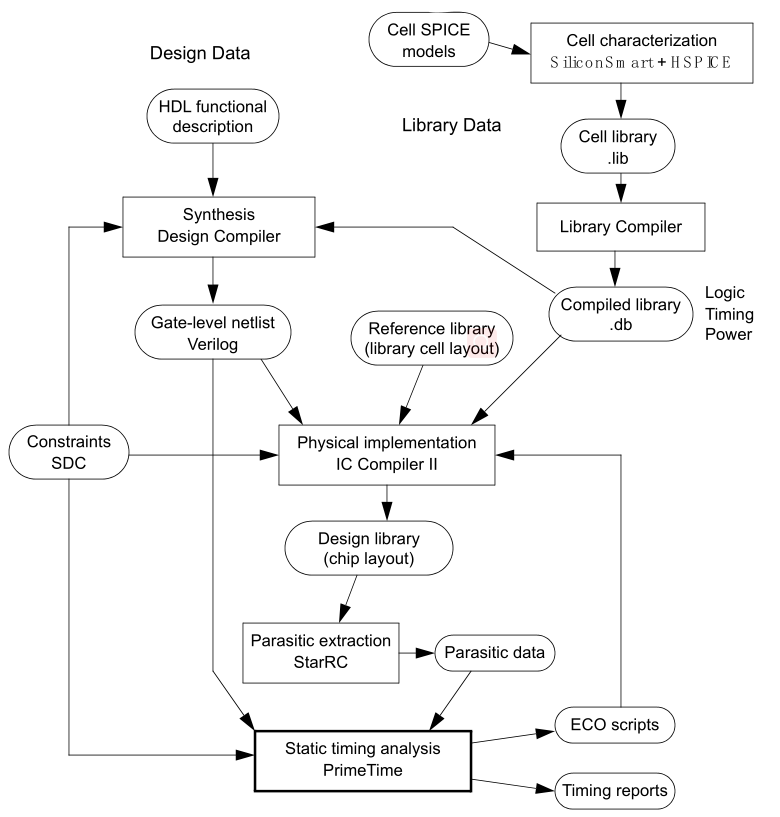

进位保留加法器和4-2压缩加法器是加法阵列中主要采用基本单元

CSA-保留进位加法器

保留进位加法器( carry-save-adder)即为一位全加器

逻辑表达式:

\begin{aligned}

& S_i=A_i \oplus B_i \oplus C_{i-1} \

& C_i=A_i B_i+C_{i-1}\left(A_i+B_i\right)

\end{aligned}

CSA电路结构图![图片[1] - CSA&4-2压缩器电路设计及verilog代码 - 我的学记|刘航宇的博客 图片[1] - CSA&4-2压缩器电路设计及verilog代码 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63d5ecaeface21e9efe74b3e.jpg)

![图片[2] - CSA&4-2压缩器电路设计及verilog代码 - 我的学记|刘航宇的博客 图片[2] - CSA&4-2压缩器电路设计及verilog代码 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63d5ee7eface21e9efeae974.jpg)

如果把保留进位加法器的进位端输出到下一级![图片[3] - CSA&4-2压缩器电路设计及verilog代码 - 我的学记|刘航宇的博客 图片[3] - CSA&4-2压缩器电路设计及verilog代码 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63d5eed7face21e9efeb9607.jpg)

这样第一级的延时为一个进位保留加法器的延时

32计数器/32压缩器

此进位保留加法器输入3个一位的数据A、B、Ci; 输出两个1位的数据D、Co。

代数运算式如下: Co*2+D=A+B+Ci

●非常明显,保留进位加法器为一计数器--计算输入信号中“1”的个数,计数值由Co、D指示,且:

●Co权值为2; A、B、Ci、D权值为1。

●其逻辑表达式如下:

\begin{aligned}

& D=A @ B @ C i \

& C o=A \& B \# A \& C i \# C i \& A

\end{aligned}

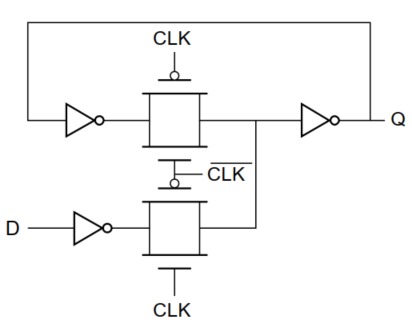

5-3计数器/53压缩器

●CSA将3个数据转换成2个数据为3-2计数器,如果能把5个数据转换成3个数据则称之为5-3计数器。

●它有五个输入端: I0、I1、I2、I3、Ci; 三个输出端: D、C、Co。

●代数运算式如下:

$$ D+C * 2+C_0 * 2=10+11+12+13+C i $$

即: I0、 l1、 12、13、Ci、D权值为1; C、Co权值为2。

其真值表如下页:![图片[4] - CSA&4-2压缩器电路设计及verilog代码 - 我的学记|刘航宇的博客 图片[4] - CSA&4-2压缩器电路设计及verilog代码 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63d5fe76face21e9ef0c1356.jpg)

![图片[5] - CSA&4-2压缩器电路设计及verilog代码 - 我的学记|刘航宇的博客 图片[5] - CSA&4-2压缩器电路设计及verilog代码 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63d5ff0aface21e9ef0d3345.jpg)

有数据表示优化后的结构可以减小门延时,传统结构为2个CSA延时,而优化后的延时大约为1.5个CSA延时

4-2压缩器

●如果连续的两个高低位5-3计数器之间Ci和Co级联的话,则称为4-2压缩加法器

●如下图![图片[6] - CSA&4-2压缩器电路设计及verilog代码 - 我的学记|刘航宇的博客 图片[6] - CSA&4-2压缩器电路设计及verilog代码 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63d5ffcbface21e9ef0ea9bf.jpg)

42压缩加法器

![图片[7] - CSA&4-2压缩器电路设计及verilog代码 - 我的学记|刘航宇的博客 图片[7] - CSA&4-2压缩器电路设计及verilog代码 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63d60011face21e9ef0f43a9.jpg)

●对于更多位的部分积也有其他的一些结构树,结构的选取要考虑到电路结构的规整

性对后端布局的影响。

●左边延时比较小但结构不规整。右边正好相反有时候会选取一些折中的结构。

Verilog代码

//-----------------------------------------------------------------------

//module : compressor42

//Description : The function of this module is to compress the partial product

//-----------------------------------------------------------------------

//author : li hangyu

//Email : hyliu@ee.ac.cn

//time : 01/28, 2023

//-----------------------------------------------------------------------

`timescale 1ns/1ps

module compressor42 (

in1,in2,in3,in4,cin,out1,out2,cout

);

parameter length = 8;

input [length*2-1 : 0] in1,in2,in3,in4;

input cin;

output [length*2 : 0] out1,out2;

output cout;

wire [length*2-1 : 0] w1,w2,w3;

assign w1 = in1 ^ in2 ^ in3 ^ in4;

assign w2 = (in1 & in2) | (in3 & in4);

assign w3 = (in1 | in2) & (in3 | in4);

assign out2 = { w1[length*2-1] , w1} ^ {w3 , cin};

assign cout = w3[length*2-1];

assign out1 = ({ w1[length*2-1] , w1} & {w3 , cin}) | (( ~{w1[length*2-1] , w1}) & { w2[length*2-1] , w2});

endmodule