参考书:数字集成电路-电路、系统与设计,本文栏目对其重点进行精简化

引论

1. 数字设计中需解决的问题

摩尔定律:技术突破才能推动摩尔定律

特征尺寸:28nm是传统制程和先进制程的分界点

存储器容量:存储器的容量增大,意味着功耗增大,意味着稳定性下降(发热)。如果想要实现更大容量的突破,需要寻找新技术或者新架构使功耗不能超过功耗红线

晶圆尺寸:晶圆尺寸增加,单位硅片数量增加,所需的技术越先进,最终成品芯片价格也越低

技术突破:大直径的硅片可以大大提高成品率

2. 集成电路质量评价-重点

![图片[1] - VLSI设计基础1-数字IC引论:度量指标及版图基础 - 我的学记|刘航宇的博客 图片[1] - VLSI设计基础1-数字IC引论:度量指标及版图基础 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f70b44f144a0100720eac5.jpg)

注:

①

是取决于制造工艺复杂行参数,常取值3

②单位面积缺陷数常取值0.5~1个缺陷/cm²

③芯片成本 $=f(\text { 芯片面积 })^4$

- 稳定性与功能性

噪声:电容耦合、电感耦合、地线耦合 - ※※※【重点】性能——延时tp、工作频率性能常与时钟周期、时钟频率相关

重点:延时![图片[2] - VLSI设计基础1-数字IC引论:度量指标及版图基础 - 我的学记|刘航宇的博客 图片[2] - VLSI设计基础1-数字IC引论:度量指标及版图基础 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f70ccff144a0100723ba40.jpg)

1、传播延时:输入和输入波形的50%翻转点之间的时间

如图:

定义传播时间tp为

$t_p=\frac{t_{p L H}+t_{p H L}}{2}$

一般而言,

①TpLH和TpHL不会完全相等

②如果要求传输延时<t,则意味着TpLH<t并且TpHL<t![图片[3] - VLSI设计基础1-数字IC引论:度量指标及版图基础 - 我的学记|刘航宇的博客 图片[3] - VLSI设计基础1-数字IC引论:度量指标及版图基础 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f7167ef144a01007347d6b.jpg)

![图片[4] - VLSI设计基础1-数字IC引论:度量指标及版图基础 - 我的学记|刘航宇的博客 图片[4] - VLSI设计基础1-数字IC引论:度量指标及版图基础 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f716b1f144a0100734f853.jpg)

2、上升时间tr

3、下降时间tf 功耗和能耗

取决的因素太多了。

常常有:瞬时功耗、峰值功耗(研究电源线尺寸)、平均功耗(研究冷却或者对电池的要求)3. 数字IC基本概念-重点

- 电压传输特性VTC(DC传输曲线)

可接受的高电压、低电压区域:VIH和VIL定义为VTC增益=-1的点 - 噪声容限=min{NMH.NML}

NMH=|VOH-VIH|

NML=|VIL-VOL| - 再生性

保证一个受干扰的信号经过若干个组合逻辑之后依旧回到一个额定电平(高或者低,不是不确定态) - 抗干扰能力

方向性

6.扇入和扇出

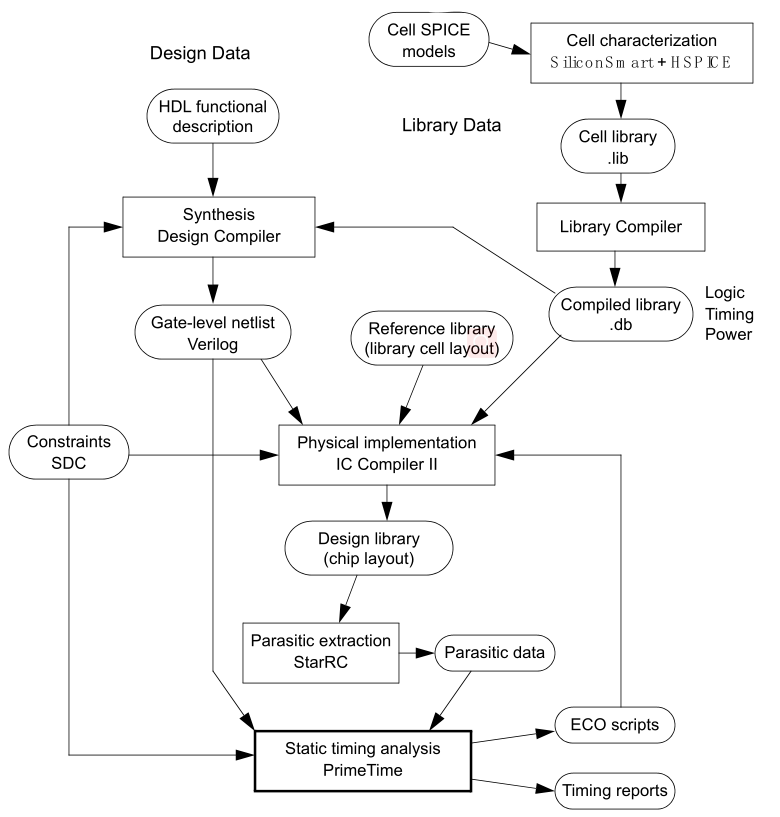

扇入和扇出个数和一些延迟有关4. IC全定制流程

![图片[5] - VLSI设计基础1-数字IC引论:度量指标及版图基础 - 我的学记|刘航宇的博客 图片[5] - VLSI设计基础1-数字IC引论:度量指标及版图基础 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f70ef1f144a01007273193.jpg)

版图基础

1. CMOS版图

1、图编辑工具:virtuoso、max

2、工艺层的概念:将cmos使用中难以理解的掩膜转化为一组简单概念化的版图层

3、可伸缩的设计:将版图所有参数定义与$\lambda$,利用EDA工具使之在想要兼容的工艺间转换。如0.25转为0.18。早期的工艺中,这个缩放比例可以达到75%左右,随着如今器件尺寸的减小,该比例只有90%左右了。

不足:①由于不同工艺之间的非线性,线性缩放仅在有限尺寸范围内;②可缩放规则是保守的,结果会使得标准单元尺寸过大或者过小。

4、晶体管的尺寸由W/L指定。

给定一个工艺,最小线宽为2$\lambda$;![图片[6] - VLSI设计基础1-数字IC引论:度量指标及版图基础 - 我的学记|刘航宇的博客 图片[6] - VLSI设计基础1-数字IC引论:度量指标及版图基础 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f70ff9f144a0100728f6f9.jpg)

5、在版图中,只要多晶硅穿过扩散区,就形成一个晶体管

随着工艺的发展,电源电压VDD呈现下降趋势。2. 设计规则检查

设计规则检查工具:Calibre DRC

设定规则的目的:可以很容易的把电路的概念转换为硅上的几何关系。

Calibre的规则相当于是行业的标准了。

其规则是基于边(edge)的DRC/LVE工具,所有的计算都是基于边来计算的,其中”边“分为”内边“和”外边“

常见的三个指令:

internal:检查多边形的内边距

external:检查多边形的外边距

enclosure:检查多边形的交迭3.棍棒图

1、要求:①将棍棒图转为管级电路图、并且写出输出表达式;②将管级电路图转化为棍棒图

2、特点:

仅用象征性的符号表示电路的拓扑结构

不需要标尺寸大小

棍棒图中棍棒的位置很重要

3、棍棒图中的串并联

以下为版图的:

串联:![图片[7] - VLSI设计基础1-数字IC引论:度量指标及版图基础 - 我的学记|刘航宇的博客 图片[7] - VLSI设计基础1-数字IC引论:度量指标及版图基础 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f710bbf144a010072a22cb.jpg)

并联:![图片[8] - VLSI设计基础1-数字IC引论:度量指标及版图基础 - 我的学记|刘航宇的博客 图片[8] - VLSI设计基础1-数字IC引论:度量指标及版图基础 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f710cef144a010072a4a77.jpg)