参考书:数字集成电路-电路、系统与设计,本文栏目对其重点进行精简化

1. 互连参数

- 导线材料

金属层

多晶硅层

n+或p+扩散层 - 互连参数——电容

平板电容模型

边缘电容模型 - 互连参数——电阻

方块电阻:![图片[1] - VLSI设计基础3-导线与互联问题 - 我的学记|刘航宇的博客 图片[1] - VLSI设计基础3-导线与互联问题 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f735b8f144a0100769800b.jpg)

扩展:

芯片中的互连,一般高层的金属层一般W较大,于是电阻更小。

即W↑→R↓→功耗P↓,RC↓

因此高层金属层,如M4、M5,常用于时钟、电源等关键信号的

布线中间层金属用作于信号线。 互连参数——电感

当频率上GHZ的时候,才会去考虑电感的作用。2. 导线模型

模型

理想导线:一般用于较大尺寸的工艺中

集总模型

适用情况:电阻小;开关频率中低水平

内容:将一条导线上的电容集总成一个电容

集总RC模型

适用情况:电阻较大,不可忽略;开关频率中低水平

内容:将一条导线上的电容集总成一个电容,电阻集总成一个电阻

不足:当互连线太长时,该模型当变得保守![图片[2] - VLSI设计基础3-导线与互联问题 - 我的学记|刘航宇的博客 图片[2] - VLSI设计基础3-导线与互联问题 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f7369af144a010076aca4e.jpg)

分布RC模型(重点)

适用情况:互连线长;导线电阻、电容不可忽略

根据推导可知,一条导线的延时同他的长度呈现二次方关系

和集总RC模型对比

分布RC模型得到的延时是集总RC模型的1/2

适用于长互连线![图片[3] - VLSI设计基础3-导线与互联问题 - 我的学记|刘航宇的博客 图片[3] - VLSI设计基础3-导线与互联问题 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f736fdf144a010076b512e.jpg)

![图片[4] - VLSI设计基础3-导线与互联问题 - 我的学记|刘航宇的博客 图片[4] - VLSI设计基础3-导线与互联问题 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f737e0f144a010076cb042.jpg)

![图片[5] - VLSI设计基础3-导线与互联问题 - 我的学记|刘航宇的博客 图片[5] - VLSI设计基础3-导线与互联问题 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f7387df144a010076dc7eb.jpg)

![图片[6] - VLSI设计基础3-导线与互联问题 - 我的学记|刘航宇的博客 图片[6] - VLSI设计基础3-导线与互联问题 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f738aff144a010076e3754.jpg)

传输线模型

适用情况:高频、射频、微波;互连材料好,其导线电阻保持在一定范围内。

内容:高频情况下,需要考虑电感的作用3. 总结

![图片[7] - VLSI设计基础3-导线与互联问题 - 我的学记|刘航宇的博客 图片[7] - VLSI设计基础3-导线与互联问题 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f7387df144a010076dc7eb.jpg)

互连问题

寄生参数对于电路的危害:

影响信号的完整性

降低信号的性能

增加延时

增加功耗

寄生的类型——电容、电阻、电感1. 电容寄生效应

此处讨论电容寄生主要是串扰

- 串扰的定义:

由相邻的信号线之间不希望有的耦合引起的干扰

小贴士:

耦合有多种,常常是电容性的耦合

串扰引起的噪声难以捕捉 - 串扰的危害

串扰将使得导线的延时难以预见,故产生了下文“可预见的导线延时设计” - 可预见的导线设计

估计改进

方法:不断参数提取,不断仿真,不断优化

缺点:设计过程需要多次重复,时间长

备注:最常用

能动性的版图生成

布线程序考虑相邻导线的作用

缺点:主要由EDA工具完成,在如今EDA工具的要求高

备注:有吸引力;已经有一些EDA工具具备该功能

可预测的结构

方法:密集型布线结构——同层信号线使用电源线隔离,相邻层采用垂直布线。

缺点:面积和电容增加了+5%,功耗和延时增加

优点:减小了电容串扰,延时差别也下降到不超过2%![图片[8] - VLSI设计基础3-导线与互联问题 - 我的学记|刘航宇的博客 图片[8] - VLSI设计基础3-导线与互联问题 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f7398bf144a010077027ec.jpg)

克服电容串扰的方法

尽量避免浮空节点,对串扰敏感的节点,加保持器降低阻抗、

敏感节点应当很好地与全摆幅信号隔离

在满足时序约束的范围内尽可能加大上升(下降)时间

在敏感的低摆幅布线网络中采用差分信号传输方法

不要使两条信号线之间的电容太大

在两个信号之间增加屏蔽线(即加GND或VDD),使线间电容变成接地电容来消除串扰,但增加了电容负载

使用屏蔽层GND或VDD2. 电阻寄生效应

- 总论

原因:芯片尺寸的减小,使得线宽减小,导线电阻增加,导线压降增加。

常考虑:电源网络设计——导线消耗了电压,使得供给门电路的电压下降

供给门电路的电压下降的危害

噪声容限降低

延时增加 降低电迁移的方法

改变金属线属性。

如合金或者Cu代替Al导线,但是成本增加。

降低温度。

降低温度可以减小电迁移发射概率。

芯片封装上面需要考虑散热问题。

增加线宽。

增加线宽可以降低平均电流密度。

缺点;增加布线资源,成本增加

优点:增加线宽不仅可以降低平均电流密度,还可以降低金属温度,间接又抑制了电迁移。3. 性能——长导线延时

- 总论

原因:根据导线模型——分布RC模型,可知$t_p \propto L^2$。为了降低电路延时,提高电路的响应速度,需要降低导线寄生电阻。 - 降低长导线延时的方法

采用更好的互连材料。

导线:铜、合金等;绝缘材料:低介电常数的材料

※但是,这种方法不是解决长导线延时的根本方法。

增加互连金属层的数目

管子数目增多驱动这金属层数目增多。

局部线(底层金属层做信号传输)采用高密度,全局线(高层金属层走全局信号,如时钟线、电源线)

采用更好的互连策略——对角线法![图片[9] - VLSI设计基础3-导线与互联问题 - 我的学记|刘航宇的博客 图片[9] - VLSI设计基础3-导线与互联问题 - 我的学记|刘航宇的博客](https://pic.imgdb.cn/item/63f73b08f144a0100772611a.jpg)

采用对角线式布线(如上图),现场可较小29%,但是对于EDA工具、掩膜制作的要求高,难度大。

目前一般采用曼哈顿式布线,即横平竖直式的布线。

中间插入中继器——中继器

长的互连线中插入中继器(如inv buffer),强行减小导线长度。但是中继器也存在延时。

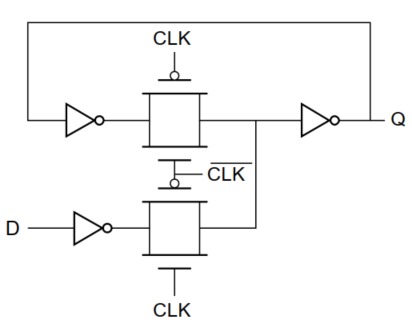

优化互连结构——寄存器或锁存器

方法:导线流水线——长互连线中插入寄存器或者锁存器,将导线分成K段。

优点:可以提高数据处理能力。每段导线中可以加入中继器进行进一步优化。